Опубликована вторая редакция проекта Vortex, развивающего открытый GPGPU на базе архитектуры набора команд RISC-V, рассчитанный на выполнение параллельных вычислений с использованием API OpenCL и модели выполнения SIMT (Single Instruction, Multiple Threads). Проекта также может использоваться при проведении исследований в области 3D-графики и разработки новых архитектур GPU. Схемы, описания аппаратных блоков на языке Verilog, симулятор, драйверы и сопутствующая проектная документация распространяются под лицензией Apache 2.0.

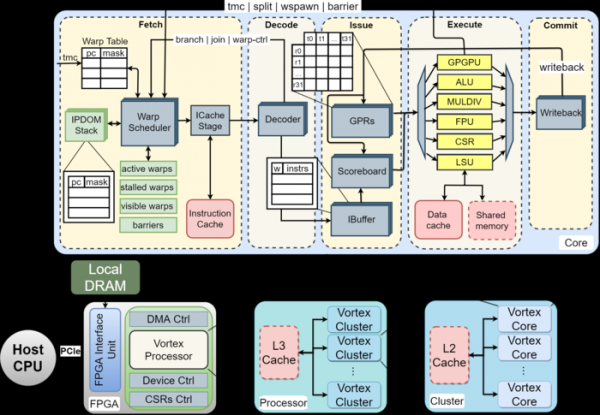

Основу GPGPU составляет типовой ISA RISC-V, расширенный некоторыми дополнительными инструкциями, необходимыми для поддержки функций GPU и управления потоками. При этом изменения в архитектуре набора команд RISC-V сведены к минимуму и по возможности используются уже имеющиеся векторные инструкции. Похожий подход применяется в проекте RV64X, который также развивает открытый GPU на базе технологий RISC-V.

Для графики на технологиях Vortex развивается открытый GPU Skybox, поддерживающий графический API Vulkan. Прототип Skybox, созданный на базе FPGA Altera Stratix 10 и включающий 32 ядра (512 потоков), позволил при частоте 230 MHz добиться производительности заливки в 3.7 гигапикселей в секунду (29.4 гигатранзакции в секунду). Отмечается, что это первый открытый GPU с программной и аппаратной реализацией, поддерживающий Vulkan.

Основные особенности Vortex:

- Поддержка 32- и 64-разрядных архитектур набора команд RISC-V RV32IMF и RV64IMAFD.

- Настраиваемое число ядер, блоков задач (warps) и потоков.

- Настраиваемое число ALU, FPU, LSU и SFU для каждого ядра.

- Настраиваемая ширина выдачи конвейера (pipeline issue width).

- Опциональная разделяемая память и кэши уровней L1, L2 и L3.

- Поддержка спецификации OpenCL 1.2.

- Возможность реализации на базе FPGA Altera Arria 10, Altera Stratix 10, Xilinx Alveo U50, U250, U280 и Xilinx Versal VCK5000.

- Расширенные инструкции: «tex» для ускорения обработки текстур, vx_rast для управления растеризацией, vx_rop для обработки фрагментов, глубины и прозрачности, vx_imadd для выполнения операции «умножить и сложить», vx_wspawn, vx_tmc и vx_bar для активации фронтов инструкций и потоков в них (wavefront, набор нитей, параллельно выполняемых SIMD Engine), vx_split и vx_join.

- Поддержка промежуточного представления шейдеров SPIR-V реализована через трансляцию в OpenCL.

- Для разработки приложений предлагается инструментарий, включающий адаптированные для работы с Vortex варианты PoCL (компилятор и runtime OpenCL), LLVM/Clang, GCC и Binutils.

- Поддерживается симуляция работы чипа с использованием Verilator (Verilog-симулятор), RTLSIM (симуляция RTL) и SimX (программная симуляция).

Среди изменений в версии Vortex 2.0:

- Проведена оптимизация микроархитектуры.

- Добавлена поддержка 64-разрядной архитектуры набора команд RISC-V RV64IMAFD.

- Добавлена возможность реализации на базе FPGA Xilinx.

- Добавлена поддержка LLVM 16 и Ubuntu 20.04.

- Проведён рефакторинг и внесены исправления недоработок, выявленных при оценке качества.

Источник: opennet.ru