Как нам известно, в марте текущего года компания TSMC приступила к опытному выпуску 5-нм продукции. Это произошло на новом заводе Fab 18 на Тайване, для выпуска 5-нм решений. Массовое производство с использованием 5-нм техпроцесса N5 ожидается во втором квартале 2020 года. До конца того же года будет налажен выпуск чипов на основе производительного 5-нм техпроцесса или N5P (performance). Наличие опытных чипов позволяет TSMC оценить возможности будущих полупроводников, выпущенных на базе нового техпроцесса, о чём компания подробно расскажет в декабре. Но кое-что можно узнать уже из поданных TSMC реферативных заявок для выступления на IEDM 2019.

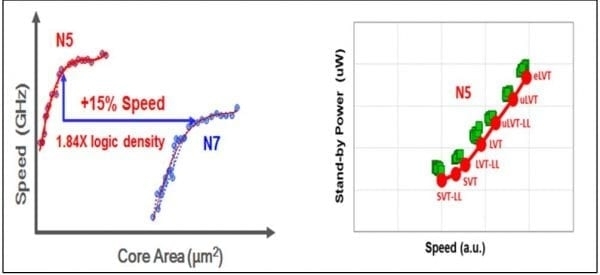

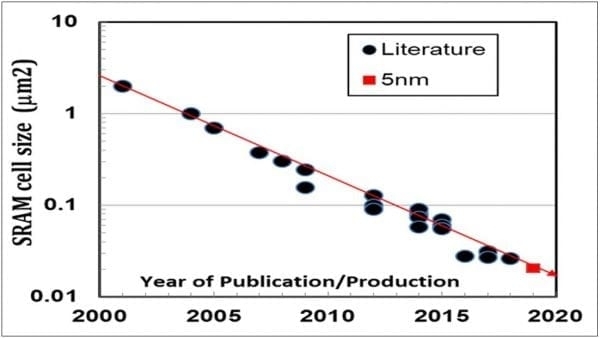

Прежде чем уточнить детали, вспомним, что нам известно из предыдущих заявлений TSMC. Утверждается, что по сравнению с 7-нм техпроцессом чистая производительность 5-нм чипов вырастет на 15 % или на 30 % сократится потребление, если производительность оставить прежней. Техпроцесс N5P добавит ещё 7 % производительности или 15 % экономии по потреблению. Плотность размещения логических элементов вырастет в 1,8 раза. Масштаб ячейки SRAM изменится в 0,75 раза.

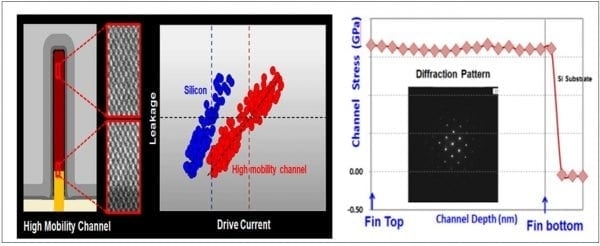

При производстве 5-нм чипов масштаб использования EUV-сканеров достигнет уровня зрелого производства. Структура канала транзистора будет изменена, возможно, за счёт использования германия вместе или вместо кремния. Это обеспечит возросшую мобильность электронов в канале и рост токов. В техпроцессе предусмотрено несколько уровней управляющих напряжения, самый высокий из которых даст прирост производительности на 25 % по сравнению с аналогичным в 7-нм техпроцессе. Питание транзисторов для интерфейсов ввода/вывода будет лежать в пределах от 1,5 В до 1,2 В.

При производстве сквозных отверстий металлизации и для контактов будут использоваться материалы с ещё меньшим сопротивлением. Для изготовления сверхвысокоплотных конденсаторов будет использоваться схема металл-диэлектрик-металл, что повысит производительность на 4 %. В общем случае TSMC перейдёт на использование новых low-K-изоляторов. В схеме обработки кремниевых пластин появится новый «сухой» процесс Metal Reactive Ion Etching (RIE), который частично заменит традиционный дамасский с использованием меди (для металлических контактов размером менее 30 нм). Также впервые для создания барьера между медными проводниками и полупроводником будет использоваться слой графена (для предотвращения электромиграции).

Из документов для декабрьского доклада на IEDM мы можем почерпнуть, что ряд параметров 5-нм чипов окажется даже лучше. Так, плотность размещения логических элементов будет выше и достигнет 1,84 крат. Также окажется меньше ячейка SRAM, площадь которой составит 0,021 мкм2. С производительностью опытного кремния всё в порядке ― получен 15-процентный прирост, как и возможно 30-процентное снижение потребления в случае замораживания верхних частот.

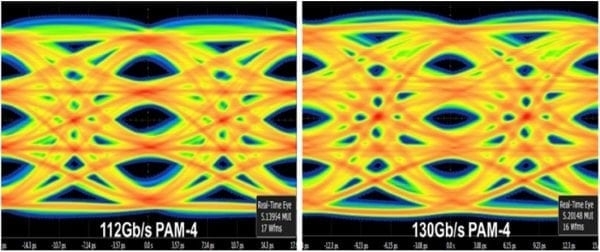

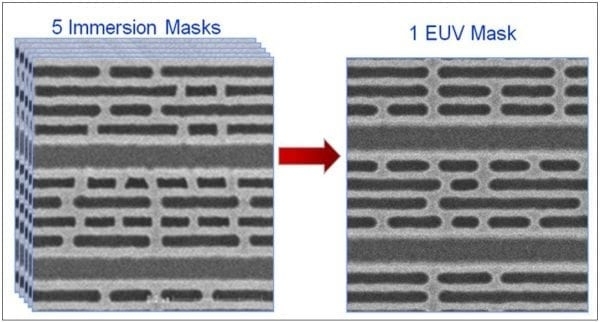

Новый техпроцесс даст возможность выбирать из семи значений управляющих напряжений, что внесёт разнообразие в процесс разработки и в продукцию, а использование сканеров EUV определённо упростит производство и сделает её дешевле. По данным TSMC, переход на EUV-сканеры обеспечивает улучшение линейного разрешения в 0,73 раза по сравнению с 7-нм техпроцессом. Например, для изготовления наиболее критичных слоёв металлизации первых слоёв вместо пяти обычных масок потребуется всего одна EUV-маска и, соответственно, всего один технологический цикл вместо пяти. Кстати, обратите внимание, насколько аккуратными получаются элементы на кристалле при использовании EUV-проекции. Красота, да и только.

Источник: 3dnews.ru