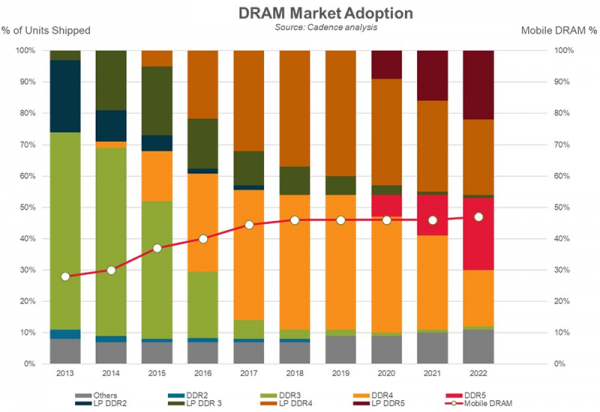

Ассоциация JEDEC до сих пор официально не опубликовала спецификацию оперативной памяти (dynamic random access memory, DRAM) следующего поколения DDR5. Но отсутствие формального документа не мешает производителям DRAM и разработчикам разнообразных систем на кристалле (system-on-chip, SoC) готовиться к её запуску. На прошлой неделе компания Cadence, разработчик аппаратного и программного обеспечения для создания микросхем, поделилась своей информацией касательно выхода DDR5 на рынок и её дальнейшего развития.

Платформы DDR5: более 12 в разработке

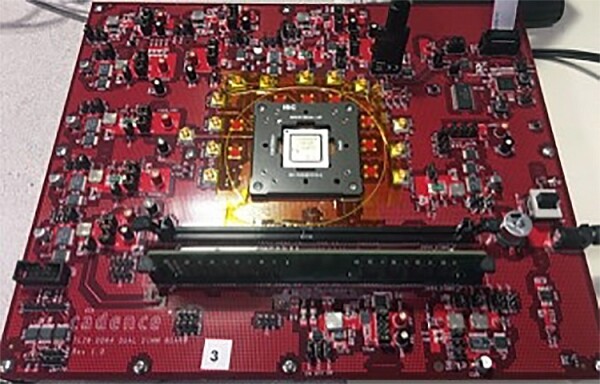

Массовость любого типа памяти определяется массовостью платформ с её поддержкой, и DDR5 не является исключением. В случае с DDR5 мы точно знаем, что её будут поддерживать процессоры AMD EPYC поколения Genoa, а также Intel Xeon Scalable поколения Sapphire Rapids, когда они будут выпущены в конце 2021 или в начале 2022 года. Компания Cadence, которая уже предлагает контроллер DDR5 и физический интерфейс (PHY) DDR5 разработчикам микросхем для лицензирования, говорит, что на данный момент в разработке находятся более дюжины SoC с поддержкой памяти следующего поколения. Часть этих систем-на-кристалле появятся раньше, часть — позже, но на данном этапе очевидно, что интерес к новой технологии весьма велик.

Специалисты Cadence уверены, что разработанные компанией контроллер DDR5 и PHY DDR5 полностью соответствуют будущей спецификации JEDEC версии 1.0, поэтому SoC, которые используют технологии Cadence, будут совместимы с модулями памяти DDR5, которые появятся позднее.

«Тесное участие в рабочих группах JEDEC является преимуществом. Мы получаем представление о том, как будет развиваться стандарт. Мы являемся поставщиком контроллеров и PHY и можем предвидеть любые потенциальные изменения на пути к окончательной стандартизации. В первые дни стандартизации мы смогли принять стандартные элементы, находящиеся в процессе разработки, и действовать вместе с нашими партнерами, чтобы получить работающий прототип контроллера и PHY. По мере того, как мы движемся к публикации стандарта, у нас появляется всё больше доказательств того, что наш пакет интеллектуальной собственности (IP) будет поддерживать соответствующие стандарту устройства DDR5», — сказал Марк Гринберг (Marc Greenberg), директор по маркетингу DRAM IP в Cadence.

Антре́: 16-Гбит микросхемы DDR5-4800

Переход на DDR5 представляет собой серьезный вызов для производителей памяти, поскольку новый тип DRAM должен одновременно обеспечить увеличение ёмкости микросхем, повышение скорости передачи данных, рост эффективной производительности (на тактовую частоту и на канал) и одновременное снижение энергопотребления. Кроме того, ожидается, что DDR5 упростит объединение нескольких устройств DRAM в одной упаковке, и это позволит существенно увеличить ёмкость модулей памяти по сравнению с тем, что индустрия использует сегодня.

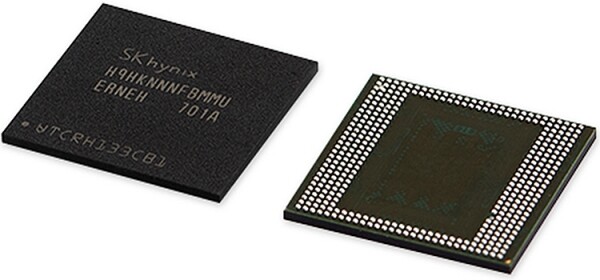

Micron и SK Hynix уже объявили о начале поставок прототипов модулей памяти на базе 16-Гбит микросхем DDR5 своим партнёрам. Компания Samsung, крупнейший в мире производитель DRAM, официально не подтверждала начало поставок прототипов, но из её анонсов на конференции ISSCC 2019 мы знаем, что компания работает с 16-Гбит микросхемами и модулями типа DDR5 (впрочем, это не значит что 8-Гбит микросхем DDR5 не будет). В любом случае, судя по всему, память DDR5 будет доступна от всех трёх крупнейших производителей DRAM при начале появления соответствующих платформ на рынке.

В Cadence уверены, что первые микросхемы типа DDR5 получат ёмкость 16 Гбит и скорость передачи данных в 4800 МегаТрансферов в секунду (МТ/с). Косвенно это было подтверждено демонстрацией модуля SK Hynix DDR5-4800 на CES 2020 вкупе с анонсом начала сэмплинга (процесс посылки прототипов продукции партнерам). От DDR5-4800 новое поколение памяти будет развиваться в двух направлениях: ёмкость и производительность.

Общие векторы развития DDR5, согласно ожиданиям Cadence:

- Ёмкость одной микросхемы начнётся с 16 Гбит, затем возрастёт до 24 Гбит (ждите модули памяти размером 24 Гбайт или 48 Гбайт), а затем до 32 Гбит.

Что касается производительности, то Cadence ожидает, что скорость передачи данных DDR5 возрастет со скорости 4800 MT/c до скорости 5200 МТ/с через 12–18 месяцев после запуска DDR4-4800, а затем до 5600 МТ/с через ещё 12–18 месяцев, поэтому повышение производительности DDR5 на серверах будет происходят с довольно регулярном ритмом.

Что касается клиентских ПК, многое будет зависеть от контроллеров памяти в микропроцессорах и поставщиков модулей памяти, но модули DIMM для энтузиастов, безусловно, будут иметь лучшие характеристики, чем используемые в серверах.

Если говорить о рынке серверов, то благодаря микросхемам с ёмкостью 16 Гбит, оптимизации внутренней архитектуры DDR5, новым серверным архитектурам и использованию модулей RDIMM вместо модулей LRDIMM, системы с одним процессорным гнездом и модулями DDR5 объемом 256 Гбайт получат значительное увеличение производительности как с точки зрения пропускной способности, так и с точки зрения задержек доступа к данным (по сравнению с современными модулями LRDIMM).

В Cadence говорят о том, что технологические усовершенствования DDR5 позволят увеличить действительную пропускную способность памяти на 36% по сравнении с DDR4 даже при скорости передачи данных 3200 МТ/с. Впрочем, когда DDR5 заработает на проектных скоростях порядка 4800 МТ/с, фактическая пропускная способность станет на 87 % выше, чем у DDR4-3200 в любом случае. Тем не менее, одной из ключевых особенностей DDR5 станет также и возможность увеличивать плотность монолитной микросхемы памяти свыше 16 Гбит.

DDR5 уже в этом году?

Как отмечалось выше, AMD Genoa и Intel Sapphire Rapids должны появиться не раньше конца 2021 года, а более вероятно — начала 2022 года. Тем не менее, господин Гринберг из Cadence уверен в оптимистичном сценарии развития событий.

Производители памяти стремятся начать массовые поставки новых типов DRAM раньше, чем станут доступны платформы. Между тем, поставки за год до того, как AMD Genoa и Intel Sapphire Rapids появятся на рынке, кажутся немного преждевременными. Но появление пробных вариантов DDR5 имеет несколько разумных объяснений: процессоры AMD и Intel, поддерживающие DDR5, ближе, чем сообщают нам процессорные компании, либо есть другие SoC с поддержкой DDR5, которые выходят на рынок.

В любом случае, если спецификация DDR5 находится на стадии окончательного черновика, крупные производители DRAM могут начать массовое производство даже без опубликованного стандарта. Теоретически, разработчики SoC также могут начать отправлять свои разработки в производство уже на этом этапе. Между тем, трудно представить, что DDR5 захватит сколько-нибудь значительную долю рынка в 2020 — 2021 гг. без поддержки со стороны основных поставщиков процессоров.

Источник: 3dnews.ru