Een tree vorentoe, twee tree terug. As omtrent 'n NAND-flitssel met 16 bisse geskryf aan elkeen , dan kan en moet ons praat oor die skryf van vyf stukkies in 'n sel. En hulle sê. By die Flash Memory Summit 2019, Toshiba die idee om 'n 5-bis NAND PLC sel vry te stel as die volgende stap na die bemeestering van die produksie van NAND QLC geheue.

Die oorgang na NAND PLC-geheue sal nog 25% by die kapasiteit van flitsskikkings voeg in vergelyking met NAND QLC. Byna uit die bloute en vir dieselfde geld sal 'n 256 GB SSD in 'n 320 GB een verander. Die slytasieweerstand, betroubaarheid en spoed van flitsgeheue sal egter daaronder ly. Dit is onwaarskynlik dat dit die bedryf sal stop. Dit is net dat aandrywers met NAND PLC-geheue die kern sal wees van daardie oplossings waar gereelde herskryf nie nodig is nie, maar toegangspoed is belangrik. Byvoorbeeld, vir die opname van argiewe. Hy speel in dieselfde hekke , wanneer musiek, flieks en ander kategorieë data streng in hul voorafbepaalde geheue-areas opgeneem word.

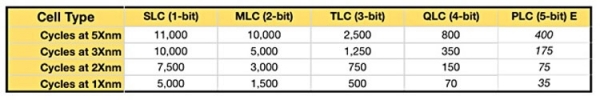

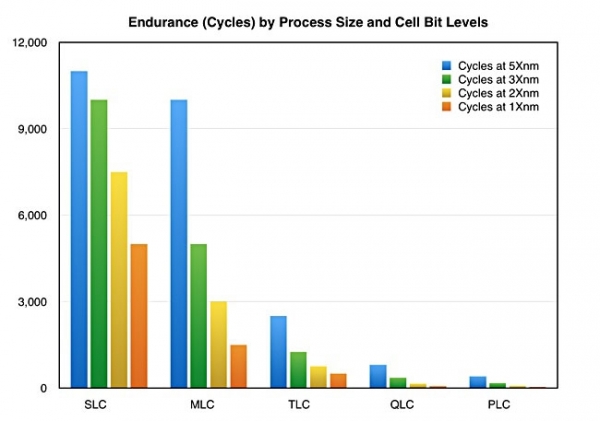

Die verwagte slytasieweerstand van NAND PLC geheue sal afneem vir die 10 nm klas proses tegnologie van 70 herskryf (vee) siklusse na 35 siklusse. Vir 3D NAND-geheue kan hierdie getalle hoër wees, aangesien die produksie daarvan groter tegnologiese prosesse gebruik. Die aantal siklusse kan verhoog word deur beheerders meer kompleks te maak in terme van meer komplekse foutkorreksieblokke, maar die beheerder sal reeds die taak hê om nie 'n 16-vlak sein in 'n QLC-sel te dekodeer nie, maar 'n 32-vlak sein in 'n PLC sel.

Jy moet ook verstaan dat daar selfs minder spasie vir laai (vlakopname) in 'n PLC-sel sal wees as in 'n QLC-sel, of die selarea vir 32-vlak-opname sal vergroot moet word. As dit nie gedoen word nie, sal die betroubaarheid van die opname afneem of die kontroleerder sal meer ingewikkeld raak. In 'n woord, daar is iets om oor te praat. As die bedryf besluit om oor te skakel na geheue met 'n vyf-bis sel, sal dit eers in 2021 gebeur.

Bron: 3dnews.ru