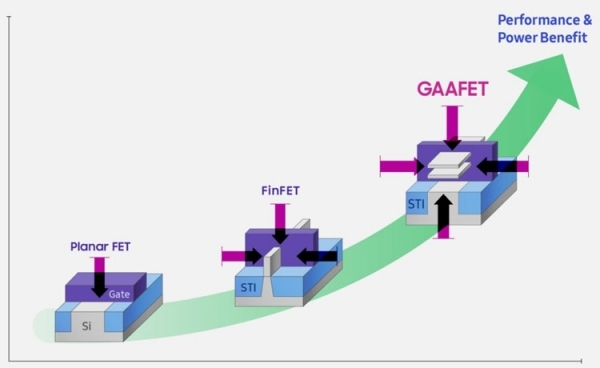

Как мы знаем, переход на техпроцесс с нормами 3 нм будет сопровождаться переходом на новую архитектуру транзистора. В терминах компании Samsung, например, это будут транзисторы MBCFET (Multi Bridge Channel FET), у которых транзисторный канал будет выглядеть как несколько расположенных друг над другом каналов в виде наностраниц, окружённых со всех сторон затвором (подробнее см. в ).

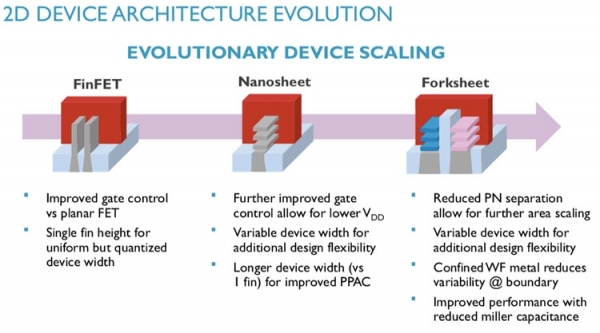

По мнению разработчиков из бельгийского центра Imec это прогрессивная, но не идеальная структура транзистора с использованием вертикальных затворов FinFET. Идеальной для техпроцессов с масштабом элементов менее 3 нм будет , которую предложили бельгийцы.

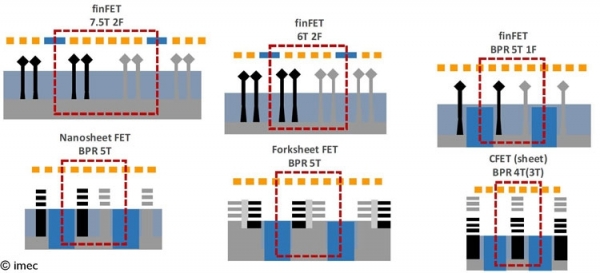

В Imec разработали транзистор с раздельными страницами или Forksheet. Это те же вертикальные наностраницы в качестве каналов транзисторов, но разделённые вертикальным диэлектриком. С одной стороны диэлектрика создаётся транзистор с n-каналом, с другой ― с p-каналом. И оба они окружены общим затвором в виде вертикального ребра.

Сократить расстояние на кристалле между транзисторами с разной проводимостью ― вот ещё один главный вызов для дальнейшего снижения масштаба технологического процесса. Моделирование TCAD подтвердило, что транзистор с раздельными страницами обеспечит 20-процентное уменьшение площади кристалла. В общем случае новая архитектура транзистора снизит стандартную высоту логической ячейки до 4,3 треков. Ячейка станет проще, что также относится к изготовлению ячейки памяти SRAM.

Простой переход от наностраничного транзистора к транзистору с раздельными наностраницами обеспечит рост производительности на 10 % с сохранением потребления или сокращение потребления на 24 % без прироста производительности. Моделирование для 2-нм техпроцесса показало, что ячейка SRAM с использованием раздельных наностраниц обеспечит комбинированное уменьшение площади и повышение производительности до 30 % при разнесении переходов p- и n- до 8 нм.

Источник: 3dnews.ru