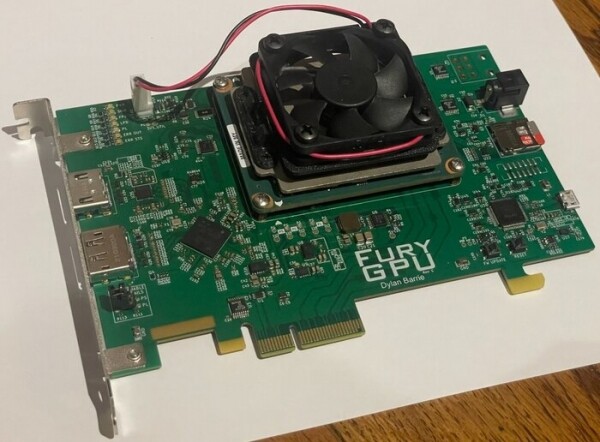

Представлен рабочий прототип проекта FuryGpu, развивающего самодельный GPU на основе FPGA Xilinx Zynq UltraScale+, оформленный в виде отдельной платы, подключаемой к ПК через интерфейс PCIe. Описания аппаратных блоков реализованы на языке SystemVerilog, а проект платы подготовлен в свободной системе автоматизированного проектирования печатных плат KiCAD. В текущем виде GPU FuryGpu уже позволяет запустить игру Quake с производительностью отрисовки 60 FPS при разрешении 1280 x 720.

Проект разрабатывается с 2021 года в качестве хобби программистом, специализирующемся на разработке компьютерных игр и интересующимся аппаратным обеспечением. Схемы платы, Verilog-описания и драйверы пока недоступны публично, но автор проекта заявил о намерении открыть все связанные с FuryGpu наработки после согласования некоторых юридических вопросов со своим работодателем (согласование необходимо, чтобы подстраховать себя от возможных претензий со стороны работодателя).

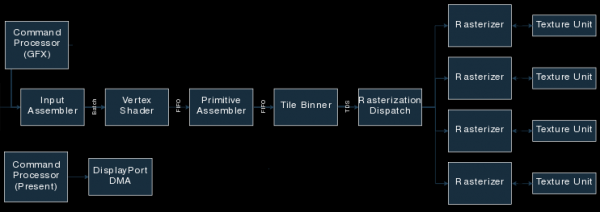

На текущей стадии развития возможности FuryGpu сравниваются с продвинутой видеокартой середины 1990-годов. Функциональность GPU определена набором фиксированных функций, выполнение программных шейдеров пока не поддерживается, а основное внимание уделяется компонентам для рендеринга, растеризации и обработки текстур. Для выполнения графических операций предоставляется собственный графический API FuryGL, напоминающий API Vulkan, но не совместимый с ним из-за отсутствия поддержки шейдеров.

Среди уже доступных возможностей:

- Четыре независимых тайловых растеризатора;

- Работа GPU на частоте 400MHz, работа блока управления текстурами на частоте 480MHz;

- Фронтэнд для выполнения операций с плавающей запятой (fp32);

- Блок маппинга и обработки текстур, поддерживающий линейную и билинейную фильтрацию с поддержкой MIP-текстурирования;

- Интерфейс PCIe Gen 2×4. Наличие портов DisplayPort и HDMI для подключения монитора.

Источник: opennet.ru