В Италии создали прототип аналогового процессора для тысячекратного ускорения обработки данных в сфере робототехники, ИИ и больших данных. Вычисления происходят в памяти процессора без пересылки данных, демонстрируя снижение потребления по сравнению с «цифрой» до 5000 раз.

Исследователи давно движутся в сторону вычислений в памяти, чтобы сократить энергетический бюджет компьютеров на пересылку данных из памяти в процессор и обратно. Это характерное для классической архитектуры фон Неймана «узкое место», которое ведёт к увеличению задержек и энергопотребления. Особенно перспективным вычисление в памяти обещает быть для реализации низкоуровневых операций линейной алгебры, требующих интенсивной обработки данных, в частности операций с матрицами и векторами.

Ранее умножение матрицы на вектор уже успешно демонстрировалось в подобных системах, тогда как реализация умножения обратной матрицы на вектор представляет собой более сложную задачу по причине высокой схемотехнической сложности. Исследователи из Миланского политехнического университета (Politecnico di Milano) представили интегрированный аналоговый ускоритель вычислений с замкнутым контуром обратной связи, предназначенный для обеих этих операций. Устройство реализовано на основе статической памяти с произвольным доступом (SRAM) и изготовлено по 90-нм КМОП-технологии.

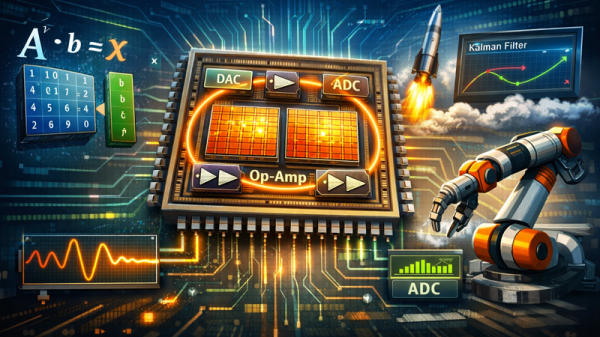

Разработанный чип содержит два массива памяти размером 64 × 64, объединённых в аналоговую петлю обратной связи с использованием встроенных операционных усилителей, цифро-аналоговых и аналого-цифровых преобразователей. Такая архитектура позволяет выполнять операции инверсии матриц непосредственно в памяти, без необходимости передачи данных во внешние вычислительные блоки. Экспериментально показано, что ускоритель способен эффективно решать системы дифференциальных уравнений методом рекурсивной блочной инверсии, демонстрируя экономию потребления до 5000 раз по сравнению с цифровыми аналогами этих цепей.

Добавим, в основе массивов памяти лежат ячейки резистивной памяти ReRAM, которые схемотехнически связаны с ячейками SRAM. Ячейка ReRAM — это безусловно аналоговый элемент, задающий тон всей новой платформе. Также следует сказать, что в основе этой европейской разработки лежат проекты учёных из Пекинского университета, которые тоже публикуют научные работы на эту же тему. В целом — это пример международного сотрудничества, которое решает общую проблему повышения эффективности высокопроизводительных вычислений.

Практическая применимость предложенного решения продемонстрирована на задачах отслеживания траектории ракеты с использованием фильтра Калмана, а также на ускорении вычислений обратной кинематики в роботизированных манипуляторах. Полученные результаты по точности сопоставимы с полностью цифровыми системами при эквивалентной разрядности, при этом аналоговый подход с вычислениями в памяти обеспечивает выигрыш по задержке, энергопотреблению и занимаемой площади кристалла.

Источник:

Источник: 3dnews.ru