A la llum de l'aproximació de la barrera en la producció d'encenalls, que és la impossibilitat de reduir l'escala dels processos tècnics, l'envasament de cristalls multixips està passant a primer pla. El rendiment dels futurs processadors es mesurarà per la complexitat, o millor encara, per la complexitat de les solucions. Com més funcions s'assignin a un xip de processador petit, més potent i eficient serà tota la plataforma. En aquest cas, el propi processador serà una plataforma d'una massa de cristalls heterogenis connectats per un bus d'alta velocitat, que no serà pitjor (en termes de velocitat i consum) que si fos un cristall monolític. En altres paraules, el processador es convertirà alhora en una placa base i en un conjunt de targetes d'expansió, incloent memòria, perifèrics, etc.

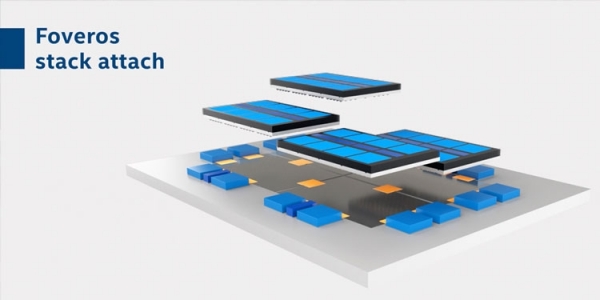

Intel ja ha demostrat la implementació de dues tecnologies patentades per a l'embalatge espacial de cristalls diferents en un sol paquet. Aquests són EMIB i . La primera és una interfície de pont integrada al substrat de "muntatge" per a la disposició horitzontal de cristalls, i la segona és una disposició tridimensional o apilada de cristalls utilitzant, entre altres coses, a través de canals de metal·lització verticals TSV. Mitjançant la tecnologia EMIB, l'empresa produeix FPGA de generació Stratix X i processadors híbrids Kaby Lake G, i la tecnologia Foveros s'implementarà en productes comercials durant la segona meitat d'aquest any. Per exemple, s'utilitzarà per produir processadors portàtils Lakefield.

Per descomptat, Intel no s'aturarà aquí i continuarà desenvolupant activament tecnologies per a l'envasament progressiu de xips. Els competidors estan fent el mateix. Com , i Samsung estan desenvolupant tecnologies per a la disposició espacial dels cristalls (chiplets) i tenen la intenció de continuar aprofitant la manta de noves oportunitats.

Recentment, a la conferència SEMICON West, Intel de nou que les seves tecnologies d'envasament multixip es desenvolupen a bon ritme. L'esdeveniment va presentar tres tecnologies, la implementació de les quals es durà a terme en un futur proper. Cal dir que les tres tecnologies no es convertiran en estàndards de la indústria. Intel guarda tots els desenvolupaments per si mateix i només els proporcionarà als clients per a la fabricació per contracte.

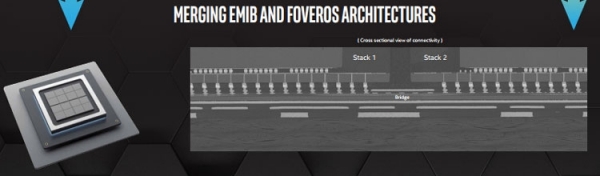

La primera de les tres noves tecnologies per a l'envasament espacial de chiplets és Co-EMIB. Aquesta és una combinació de la tecnologia d'interfície de pont EMIB de baix cost amb chiplets Foveros. Els dissenys de pila multixip de Foveros es poden interconnectar amb enllaços EMIB horitzontals en sistemes complexos sense sacrificar el rendiment o el rendiment. Intel afirma que la latència i el rendiment de totes les interfícies multicapa no serà pitjor que en un xip monolític. De fet, a causa de l'extrema densitat de cristalls heterogenis, el rendiment global i l'eficiència energètica de la solució i les interfícies seran fins i tot més grans que en el cas d'una solució monolítica.

Per primera vegada, la tecnologia Co-EMIB es podria utilitzar per produir processadors híbrids Intel per al superordinador Aurora, que s'espera que s'enviïn a finals del 2021 (un projecte conjunt entre Intel i Cray). El prototip de processador es va mostrar a SEMICON West com una pila de 18 matrius petites en una matriu gran (Foveros), un parell dels quals estaven connectats horitzontalment mitjançant una interconnexió EMIB.

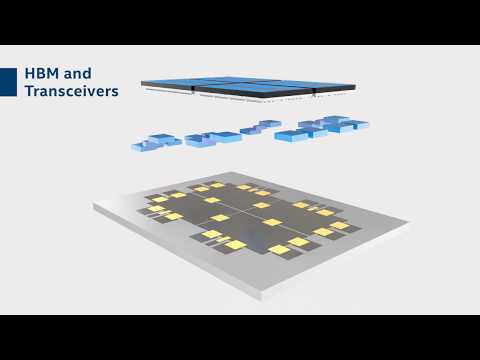

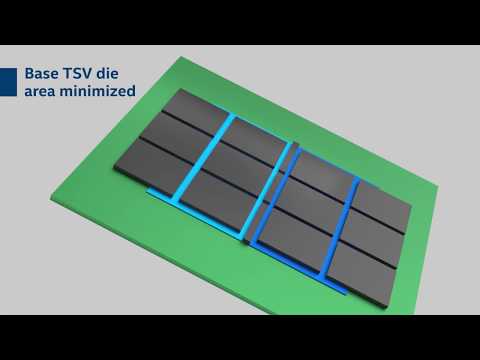

La segona de les tres noves tecnologies d'embalatge de xips espacials d'Intel s'anomena Omni-Directional Interconnect (ODI). Aquesta tecnologia no és més que l'ús de les interfícies EMIB i Foveros per a la connexió elèctrica horitzontal i vertical de cristalls. El que va fer que ODI fos un element independent va ser el fet que l'empresa va implementar una font d'alimentació per a xips a la pila mitjançant connexions TSV verticals. Aquest enfocament permetrà distribuir els aliments de manera eficaç. Al mateix temps, la resistència dels canals TSV de 70 μm per a l'alimentació es redueix significativament, cosa que reduirà el nombre de canals necessaris per subministrar energia i alliberarà l'àrea del xip per als transistors (per exemple).

Finalment, Intel va anomenar la interfície xip a xip MDIO la tercera tecnologia per a l'embalatge espacial. Aquest és l'Advanced Interface Bus (AIB) en forma de capa física per a l'intercanvi de senyals entre xips. En sentit estricte, aquesta és la segona generació del bus AIB, que Intel està desenvolupant per a DARPA. La primera generació d'AIB es va introduir el 2017 amb la capacitat de transferir dades a cada contacte a una velocitat de 2 Gbit/s. El bus MDIO proporcionarà intercanvi a una velocitat de 5,4 Gbit/s. Aquest enllaç es convertirà en un competidor del bus TSMC LIPINCON. La velocitat de transferència de LIPINCON és més alta: 8 Gbit/s, però Intel MDIO té una densitat més gran de GB/s per mil·límetre: 200 enfront de 67, per la qual cosa Intel afirma un desenvolupament que no és pitjor que el del seu competidor.

Font: 3dnews.ru