In light of the approaching barrier in the production of chips, which becomes the impossibility of further reduction in the scale of technical processes, multi-chip packaging of crystals comes to the fore. The performance of the processors of the future will be measured by the complexity, or rather, the complexity of the solutions. The more functions can be assigned to a small processor chip, the more powerful and efficient the entire platform will be. At the same time, the processor itself will be a platform from a mass of heterogeneous crystals connected by a high-speed bus, which will be no worse (in terms of speed and consumption) than if it was a single monolithic crystal. In other words, the processor will become both the motherboard and a set of expansion cards, including memory, peripherals, and more.

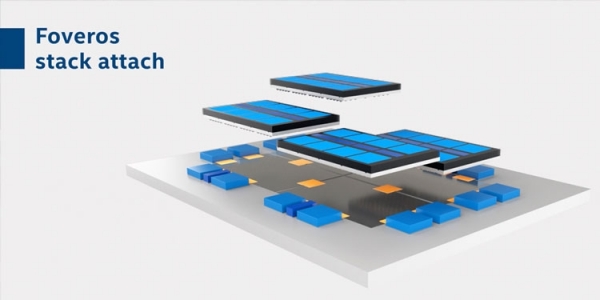

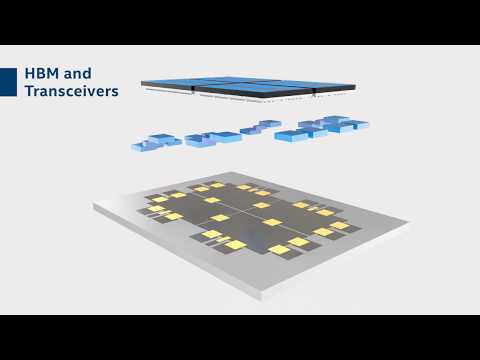

Intel has already demonstrated the implementation of two proprietary technologies for the spatial packaging of dissimilar chips in one package. These are EMIB technologies and . The first is interface bridges built into the “mounting” substrate for horizontal stacking of crystals, and the second is a three-dimensional or stacked stacking of chips using, among other things, through vertical metallization channels TSVs. Using EMIB technology, the company is launching Stratix X generation FPGAs and Kaby Lake G APUs, and Foveros technology will be implemented in commercial products in the second half of this year. For example, Lakefield notebook processors will be produced with its help.

Of course, Intel will not stop there and will continue to actively develop technologies for progressive packaging of crystals. Competitors are doing the same. How , and Samsung are developing technologies for the spatial arrangement of crystals (chiplets) and intend to further pull the blanket of new opportunities over themselves.

The other day at the SEMICON West conference, Intel again that its technology for multi-chip packaging is developing at a good pace. The event presents three technologies, the implementation of which will take place in the near future. I must say that all three technologies will not become industry standards. All developments Intel keeps for itself, and will only provide customers for contract manufacturing.

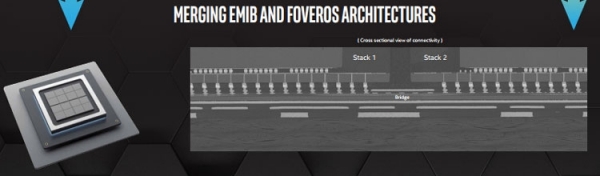

Co-EMIB was announced as the first of three new technologies for spatial packaging of chiplets. This is a combination of low-cost EMIB bridge interface technology with Foveros chiplets. Foveros multi-chip stacking designs can be interconnected by horizontal EMIB links into complex systems without compromising throughput or performance. Intel claims that the latency and throughput of all multi-level interfaces will be no worse than in a monolithic chip. In fact, due to the maximum density of dissimilar crystals, the overall performance and energy efficiency of the solution and interfaces will be even higher than in the case of a monolithic solution.

For the first time, Co-EMIB technology can be implemented for the production of Intel hybrid processors for the Aurora supercomputer, expected to ship in late 2021 (a joint project between Intel and Cray). The processor prototype was shown at SEMICON West as a stack of 18 small dies on one large die (Foveros), a pair of which were connected horizontally with an EMIB connection.

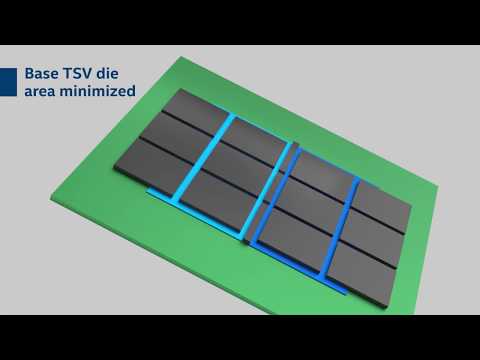

The second of Intel's three new spatial packaging technologies for chips is called Omni-Directional Interconnect (ODI). This technology is nothing but the use of EMIB and Foveros interfaces for horizontal and vertical electrical connection of crystals. The fact that the company implemented the power supply of the chipsets in the stack using vertical TSVs-connections made ODI a separate item. This approach will make it possible to effectively dilute the food. At the same time, the resistance of 70-µm TSVs channels for power supply is significantly reduced, which will reduce the number of channels required for power supply and free up chip area for transistors (for example).

Finally, Intel named the MDIO chip-to-chip interface as the third space-packing technology. This is an Advanced Interface Bus (AIB) in the form of a physical layer for inter-chip signaling. Strictly speaking, this is the second generation of the AIB bus, which Intel is developing for DARPA. The first generation of AIB was introduced in 2017 with the ability to transfer data at a rate of 2 Gbps on each pin. The MDIO bus will provide an exchange at a speed of 5,4 Gb / s. This link will compete with the TSMC LIPINCON bus. The LIPINCON exchange speed is higher - 8 Gb / s, but Intel MDIO has a higher density of GB / s per millimeter: 200 versus 67, so Intel claims a design that is no worse than that of a competitor.

Source: 3dnews.ru