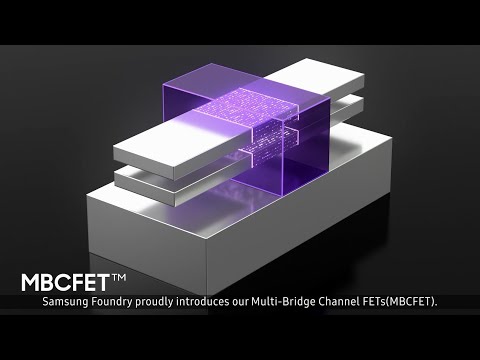

Hodiaŭ Samsung Electronics pri planoj por la disvolviĝo de teknikaj procezoj por produktado de duonkonduktaĵoj. La firmao konsideras la kreadon de ciferecaj projektoj de eksperimentaj 3-nm-blatoj bazitaj sur patentitaj MBCFET-transistoroj kiel la ĉefa nuna atingo. Tiuj estas transistoroj kun multoblaj horizontalaj nanopaĝaj kanaloj en vertikalaj FET-pordegoj (Multi-Bridge-Channel FET).

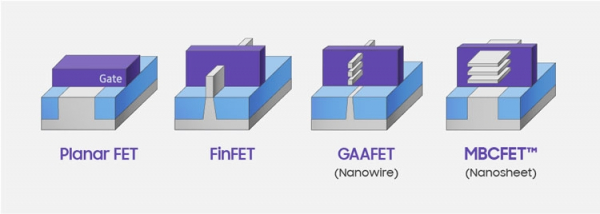

Kadre de alianco kun IBM, Samsung evoluigis iomete malsaman teknologion por la produktado de transistoroj kun kanaloj tute ĉirkaŭitaj de pordegoj (GAA aŭ Gate-All-Around). La kanaloj laŭsupoze fariĝis maldikaj en la formo de nanodratoj. Poste, Samsung malproksimiĝis de ĉi tiu skemo kaj patentis transistoran strukturon kun kanaloj en formo de nanopaĝoj. Ĉi tiu strukturo permesas kontroli la karakterizaĵojn de transistoroj manipulante kaj la nombron da paĝoj (kanaloj) kaj alĝustigante la larĝon de la paĝoj. Por klasika FET-teknologio, tia manovro estas neebla. Por pliigi la potencon de FinFET-transistoro, estas necese multobligi la nombron da FET-naĝiloj sur la substrato, kaj tio postulas areon. La karakterizaĵoj de la transistoro MBCFET povas esti ŝanĝitaj ene de unu fizika pordego, por kiu vi devas agordi la larĝon de la kanaloj kaj ilian nombron.

La havebleco de cifereca dezajno (bendigita eksteren) de prototippeceto por produktado uzanta la GAA-procezon permesis al Samsung determini la limojn de la kapabloj de MBCFET-transistoroj. Oni devas memori, ke ĉi tio ankoraŭ estas komputilaj modelaj datumoj kaj la nova teknika procezo povas esti juĝita nur finfine post kiam ĝi estis lanĉita en amasproduktadon. Tamen, ekzistas deirpunkto. La firmao diris, ke la transiro de la 7nm-procezo (evidente la unua generacio) al la GAA-procezo provizos 45%-redukton de ĵeta areo kaj 50%-redukton en konsumo. Se vi ne ŝparas en konsumo, produktiveco povas esti pliigita je 35%. Antaŭe, Samsung vidis ŝparaĵojn kaj gajnojn de produktiveco kiam moviĝis al la 3nm-procezo apartigitaj per komoj. Montriĝis, ke ĝi estis aŭ unu aŭ la alia.

La kompanio konsideras, ke la preparado de publika nuba platformo por sendependaj pecetoprogramistoj kaj senfablaj kompanioj estas grava punkto por popularigi la 3nm-procezan teknologion. Samsung ne kaŝis la evolumedion, projektan konfirmon kaj bibliotekojn sur produktadserviloj. La platformo SAFE (Samsung Advanced Foundry Ecosystem Cloud) estos disponebla por dizajnistoj tra la mondo. La SAFE-nuba platformo estis kreita kun la partopreno de tiaj gravaj publikaj nubaj servoj kiel Amazon Web Services (AWS) kaj Microsoft Azure. Programistoj de dezajnosistemoj de Cadence kaj Synopsys disponigis siajn dezajn ilojn ene de SAFE. Ĉi tio promesas faciligi kaj malmultekoste krei novajn solvojn por Samsung-procezoj.

Revenante al la 3nm-proceza teknologio de Samsung, ni aldonu, ke la kompanio prezentis la unuan version de sia blata disvolva pako - 3nm GAE PDK Versio 0.1. Kun ĝia helpo, vi povas komenci desegni 3nm-solvojn hodiaŭ, aŭ almenaŭ prepari por renkonti ĉi tiun Samsung-procezon kiam ĝi disvastiĝos.

Samsung anoncas siajn estontajn planojn jene. En la dua duono de ĉi tiu jaro, amasproduktado de blatoj uzante la 6nm-procezon estos lanĉita. Samtempe, la evoluo de la 4nm-proceza teknologio estos kompletigita. La evoluo de la unuaj Samsung-produktoj uzantaj la 5nm-procezon finiĝos ĉi-aŭtune, kun produktado lanĉo en la unua duono de la venonta jaro. Ankaŭ, antaŭ la fino de ĉi tiu jaro, Samsung kompletigos la evoluon de la 18FDS-proceza teknologio (18 nm sur FD-SOI-oblatoj) kaj 1-Gbit eMRAM-blatoj. Procezaj teknologioj de 7 nm ĝis 3 nm uzos EUV-skaniloj kun kreskanta intenseco, igante ĉiun nanometron kalkuli. Plu sur la vojo malsupren, ĉiu paŝo estos farita kun batalo.

fonto: 3dnews.ru