La Asociación JEDEC ha publicado una especificación preliminar para la memoria HBM4 de cuarta generación, que promete aumentos significativos en la capacidad y el ancho de banda para inteligencia artificial y sistemas informáticos de alto rendimiento.

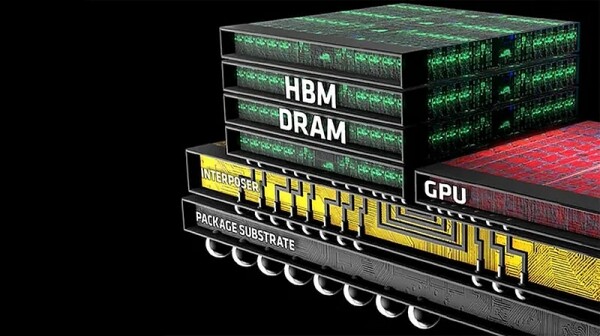

JEDEC la especificación de memoria HBM4 (memoria de alto ancho de banda) de próxima generación, acercándose a la finalización del desarrollo de un nuevo estándar DRAM, Hardware de Tom. Según los datos publicados, HBM4 admitirá una interfaz de 2048 bits por pila, aunque a una velocidad de datos menor en comparación con HBM3E. Además, el nuevo estándar proporciona una gama más amplia de capas de memoria, lo que permitirá adaptarse mejor a diferentes tipos de aplicaciones.

El nuevo estándar HBM4 admitirá pilas de 24 GB y 32 GB, y también ofrecerá configuraciones para pilas de 4, 8, 12 y 16 capas con interconexiones TSV verticales. El Comité JEDEC ha acordado provisionalmente velocidades de hasta 6,4 Gt/s, pero se están debatiendo la posibilidad de lograr velocidades de datos aún mayores.

Una pila de 16 capas basada en chips de 32 gigabits podrá proporcionar una capacidad de 64 GB, es decir, en este caso, un procesador con cuatro módulos de memoria podrá admitir 256 GB de memoria con un ancho de banda máximo de 6,56 TB/s usando una interfaz de 8192 bits.

Aunque HBM4 tendrá el doble de canales por pila en comparación con HBM3 y un tamaño físico más grande para garantizar la compatibilidad, un solo controlador podrá manejar tanto HBM3 como HBM4. Sin embargo, se necesitarán diferentes sustratos para adaptarse a diferentes factores de forma. Curiosamente, JEDEC no mencionó la posibilidad de integrar memoria HBM4 directamente en los procesadores, que es quizás el aspecto más intrigante del nuevo tipo de memoria.

Anteriormente, SK hynix y TSMC anunciaron su colaboración en el desarrollo de cristales base HBM4 y, un poco más tarde, en el Simposio Europeo 2024, TSMC confirmó que utilizará sus procesos 12FFC+ (clase de 12 nm) y N5 (clase de 5 nm) para producir estos cristales.

El proceso N5 de TSMC permite la integración de más lógica y funciones, con pasos de interconexión que varían de 9 a 6 micrones, lo cual es fundamental para la integración en el chip. El proceso 12FFC+, basado en la tecnología FinFET de 16 nm de TSMC, producirá matrices base rentables que conectan la memoria a los procesadores host mediante obleas de silicio.

Tenga en cuenta que HBM4 está diseñado principalmente para las necesidades de inteligencia artificial generativa y computación de alto rendimiento, que requieren procesar grandes cantidades de datos y realizar cálculos complejos. Por lo tanto, es poco probable que veamos HBM4 en aplicaciones cliente como las GPU. SK hynix espera iniciar la producción del HBM4 en 2026.

Fuente:

Fuente: 3dnews.ru