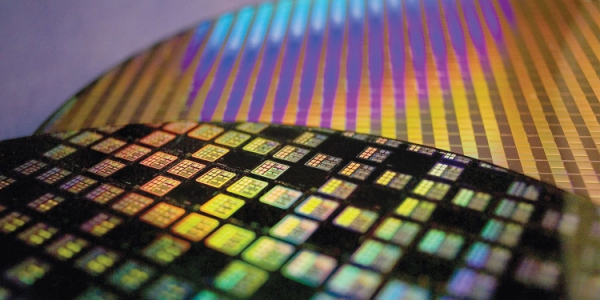

La empresa taiwanesa de semiconductores TSMC anunció que ha completado por completo el desarrollo de la infraestructura de diseño de 5 nm bajo la Plataforma de Innovación Abierta, incluidos archivos de tecnología y kits de diseño. El proceso técnico ha pasado muchas pruebas de fiabilidad de los chips de silicio. Esto permite el desarrollo de SoC de 5 nm para soluciones móviles y de alto rendimiento de próxima generación dirigidas a los mercados de rápido crecimiento de 5G y de inteligencia artificial.

La tecnología de proceso de 5 nm de TSMC ya ha alcanzado la etapa de producción de riesgo. Usando el núcleo ARM Cortex-A72 como ejemplo, en comparación con el proceso de 7 nm de TSMC, proporciona una mejora de 1,8 veces en la densidad del troquel y una mejora del 15 por ciento en la velocidad del reloj. La tecnología de 5 nm aprovecha la simplificación del proceso al cambiar completamente a la litografía ultravioleta extrema (EUV), logrando buenos avances en el aumento de las tasas de rendimiento de los chips. Hoy en día, la tecnología ha alcanzado un mayor nivel de madurez en comparación con procesos anteriores de TSMC en la misma etapa de desarrollo.

Toda la infraestructura de 5 nm de TSMC ya está disponible para descargar. Aprovechando los recursos del ecosistema de diseño abierto del fabricante taiwanés, los clientes ya han comenzado un desarrollo intensivo del diseño. Junto con sus socios Electronic Design Automation, la empresa también ha añadido otro nivel de certificación de flujo de diseño.

Fuente: 3dnews.ru