Un paso hacia adelante, dos hacia atras. Si se trata de una celda flash NAND con 16 bits escritos en cada una , entonces podemos y debemos hablar de escribir cinco bits en una celda. Y ellos dicen. En la Cumbre de Memoria Flash 2019, Toshiba la idea de lanzar una celda PLC NAND de 5 bits como siguiente paso después de dominar la producción de memoria NAND QLC.

La transición a la memoria NAND PLC agregará otro 25% a la capacidad de las matrices flash en comparación con NAND QLC. Casi de la nada y por el mismo dinero, un SSD de 256 GB se convertirá en uno de 320 GB. Sin embargo, la resistencia al desgaste, la confiabilidad y la velocidad de la memoria flash se verán afectadas. Es poco probable que esto detenga la industria. Simplemente las unidades con memoria NAND PLC estarán en el corazón de aquellas soluciones donde no es necesaria una reescritura frecuente, pero la velocidad de acceso es importante. Por ejemplo, para grabar archivos. Él juega en las mismas puertas. , cuando la música, las películas y otras categorías de datos se graban estrictamente en sus áreas de memoria predeterminadas.

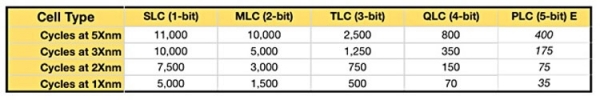

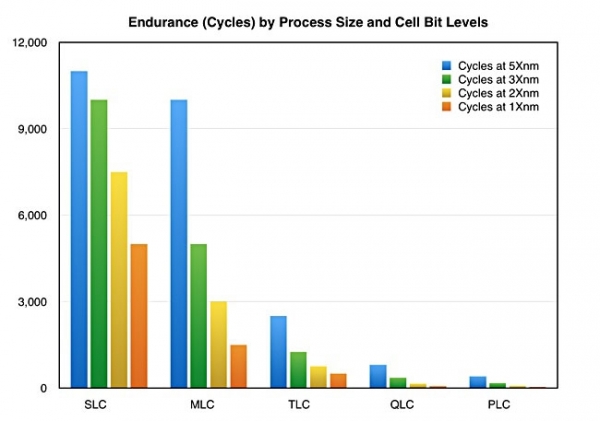

La resistencia al desgaste esperada de la memoria NAND PLC disminuirá para la tecnología de proceso de clase de 10 nm de 70 ciclos de reescritura (borrado) a 35 ciclos. Para la memoria 3D NAND, estas cifras pueden ser mayores, ya que su producción utiliza procesos tecnológicos más amplios. El número de ciclos se puede aumentar haciendo que los controladores sean más complejos en términos de bloques de corrección de errores más complejos, pero el controlador ya tendrá la tarea de decodificar no una señal de 16 niveles en una celda QLC, sino una señal de 32 niveles en una Célula PLC.

También debe comprender que habrá incluso menos espacio para la carga (grabación de niveles) en una celda PLC que en una celda QLC, o será necesario aumentar el área de la celda para la grabación de 32 niveles. Si no se hace esto, la fiabilidad de la grabación disminuirá o el controlador se volverá más complicado. En una palabra, hay de qué hablar. Si la industria decide pasar a la memoria con una celda de cinco bits, esto no sucederá hasta 2021.

Fuente: 3dnews.ru