امروز سامسونگ الکترونیک در مورد برنامه هایی برای توسعه فرآیندهای فنی برای تولید نیمه هادی ها. این شرکت ایجاد پروژه های دیجیتال تراشه های آزمایشی 3 نانومتری بر اساس ترانزیستورهای MBCFET ثبت شده را دستاورد اصلی فعلی می داند. این ترانزیستورها با کانال های نانوصفحه افقی متعدد در گیت های FET عمودی (Multi-Bridge-Channel FET) هستند.

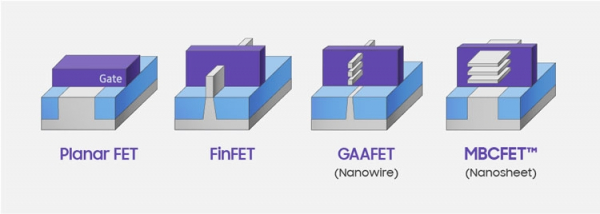

به عنوان بخشی از اتحاد با IBM، سامسونگ یک فناوری کمی متفاوت برای تولید ترانزیستور با کانال های کاملاً احاطه شده توسط دروازه ها (GAA یا Gate-All-Around) توسعه داد. قرار بود کانال ها به شکل نانوسیم نازک ساخته شوند. متعاقباً، سامسونگ از این طرح فاصله گرفت و یک ساختار ترانزیستوری با کانال هایی به شکل صفحات نانو را به ثبت رساند. این ساختار به شما اجازه می دهد تا با دستکاری تعداد صفحات (کانال ها) و با تنظیم عرض صفحات، ویژگی های ترانزیستورها را کنترل کنید. برای فناوری FET کلاسیک، چنین مانوری غیرممکن است. برای افزایش قدرت ترانزیستور FinFET باید تعداد پره های FET روی زیرلایه را چند برابر کرد و این مستلزم مساحت است. ویژگی های ترانزیستور MBCFET را می توان در یک گیت فیزیکی تغییر داد که برای آن باید عرض کانال ها و تعداد آنها را تنظیم کنید.

در دسترس بودن طرح دیجیتال (برداشت شده) از یک نمونه اولیه تراشه برای تولید با استفاده از فرآیند GAA به سامسونگ این امکان را میدهد که محدودیتهای قابلیتهای ترانزیستورهای MBCFET را تعیین کند. باید در نظر داشت که این هنوز دادههای مدلسازی کامپیوتری است و فرآیند فنی جدید تنها پس از راهاندازی به تولید انبوه در نهایت قابل قضاوت است. با این حال، یک نقطه شروع وجود دارد. این شرکت گفت که انتقال از فرآیند 7 نانومتری (بدیهی است که نسل اول) به فرآیند GAA باعث کاهش 45 درصدی سطح قالب و کاهش 50 درصدی در مصرف خواهد شد. اگر در مصرف صرفه جویی نکنید، بهره وری را می توان تا 35 درصد افزایش داد. پیش از این، سامسونگ در هنگام انتقال به فرآیند 3 نانومتری شاهد صرفه جویی و افزایش بهره وری بود با کاما از هم جدا می شوند. معلوم شد که یا یکی است یا دیگری.

این شرکت آماده سازی یک پلت فرم ابر عمومی برای توسعه دهندگان تراشه های مستقل و شرکت های فابلس را نکته مهمی در رواج فناوری فرآیند 3 نانومتری می داند. سامسونگ محیط توسعه، تأیید پروژه و کتابخانه ها را در سرورهای تولید پنهان نکرده است. پلت فرم SAFE (سامسونگ پیشرفته Foundry Ecosystem Cloud) در دسترس طراحان سراسر جهان خواهد بود. پلتفرم ابری SAFE با مشارکت خدمات ابر عمومی بزرگ مانند خدمات وب آمازون (AWS) و Microsoft Azure ایجاد شد. توسعه دهندگان سیستم های طراحی از Cadence و Synopsys ابزار طراحی خود را در SAFE ارائه کردند. این نوید می دهد که ایجاد راه حل های جدید برای فرآیندهای سامسونگ آسان تر و ارزان تر شود.

با بازگشت به فناوری فرآیند 3 نانومتری سامسونگ، اضافه کنیم که این شرکت اولین نسخه از بسته توسعه تراشه خود - 3 نانومتری GAE PDK نسخه 0.1 را ارائه کرد. با کمک آن، میتوانید از امروز شروع به طراحی راهحلهای 3 نانومتری کنید، یا حداقل خود را برای پاسخگویی به این فرآیند سامسونگ در زمان فراگیر شدن آماده کنید.

سامسونگ برنامه های آینده خود را به شرح زیر اعلام می کند. در نیمه دوم سال جاری تولید انبوه تراشه ها با استفاده از فرآیند 6 نانومتری راه اندازی می شود. در همان زمان، توسعه فناوری فرآیند 4 نانومتری تکمیل خواهد شد. توسعه اولین محصولات سامسونگ با استفاده از فرآیند 5 نانومتری پاییز امسال تکمیل می شود و تولید آن در نیمه اول سال آینده آغاز می شود. همچنین، تا پایان سال جاری، سامسونگ توسعه فناوری فرآیند 18FDS (18 نانومتر بر روی ویفرهای FD-SOI) و تراشههای 1 گیگابیت eMRAM را تکمیل خواهد کرد. فناوریهای فرآیندی از 7 تا 3 نانومتر از اسکنرهای EUV با شدت فزاینده استفاده میکنند و هر نانومتر را به حساب میآورند. در ادامه مسیر پایین، هر قدمی با مبارزه برداشته خواهد شد.

منبع: 3dnews.ru