Alla luce dell’avvicinarsi dell’ostacolo nella produzione di chip, ovvero l’impossibilità di un ulteriore ridimensionamento dei processi tecnici, sta diventando sempre più importante il confezionamento multi-chip di cristalli. Le prestazioni dei futuri processori verranno misurate dalla complessità, o meglio ancora, dalla complessità delle soluzioni. Più funzioni vengono assegnate a un piccolo chip del processore, più potente ed efficiente risulterà l'intera piattaforma. In questo caso, il processore stesso sarà una piattaforma composta da una massa di cristalli eterogenei collegati da un bus ad alta velocità, che non sarà peggiore (in termini di velocità e consumo) che se fosse un cristallo monolitico. In altre parole, il processore diventerà sia una scheda madre che un insieme di schede di espansione, inclusa memoria, periferiche e così via.

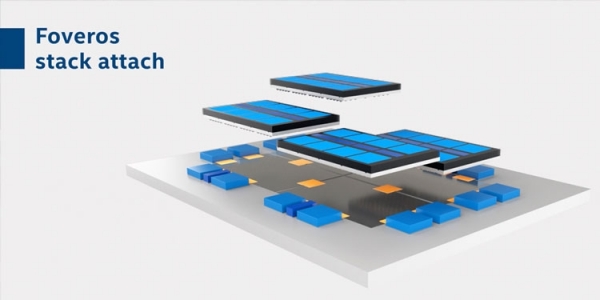

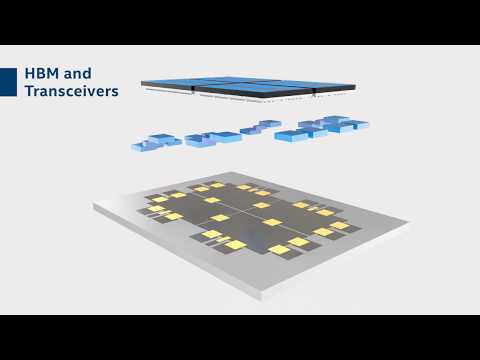

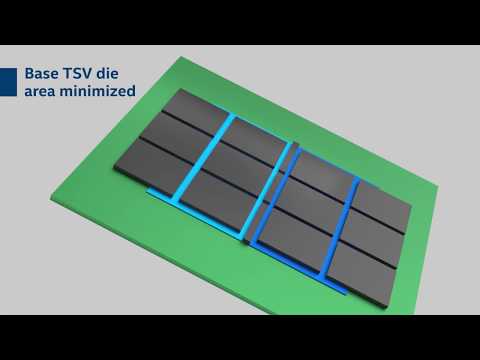

Intel ha già dimostrato l'implementazione di due tecnologie proprietarie per il confezionamento spaziale di cristalli diversi in un unico pacchetto. Questi sono EMIB e . La prima è costituita da interfacce a ponte integrate nel substrato di "montaggio" per la disposizione orizzontale dei cristalli, e la seconda è una disposizione tridimensionale o impilata dei cristalli che utilizza, tra le altre cose, attraverso canali di metallizzazione verticale TSV. Utilizzando la tecnologia EMIB, l'azienda produce FPGA della generazione Stratix X e processori ibridi Kaby Lake G, e la tecnologia Foveros sarà implementata in prodotti commerciali nella seconda metà di quest'anno. Ad esempio, verrà utilizzato per produrre processori per laptop Lakefield.

Naturalmente, Intel non si fermerà qui e continuerà a sviluppare attivamente tecnologie per il packaging progressivo dei chip. I concorrenti stanno facendo la stessa cosa. Come e Samsung stanno sviluppando tecnologie per la disposizione spaziale dei cristalli (chiplet) e intendono continuare a coprire nuove opportunità.

Recentemente, alla conferenza SEMICON West, di nuovo Intel che le sue tecnologie per il confezionamento multi-chip si stanno sviluppando a un buon ritmo. L'evento ha presentato tre tecnologie, la cui implementazione avverrà nel prossimo futuro. Va detto che tutte e tre le tecnologie non diventeranno standard del settore. Intel mantiene tutti gli sviluppi per sé e li fornirà ai clienti solo per la produzione a contratto.

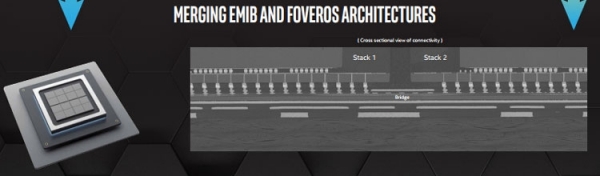

La prima delle tre nuove tecnologie per il confezionamento spaziale dei chiplet è Co-EMIB. Si tratta di una combinazione della tecnologia di interfaccia bridge EMIB a basso costo con i chiplet Foveros. I progetti di stack multi-chip di Fovero possono essere interconnessi con collegamenti EMIB orizzontali in sistemi complessi senza sacrificare il throughput o le prestazioni. Intel afferma che la latenza e il throughput di tutte le interfacce multistrato non saranno peggiori di quelli di un chip monolitico. Infatti, a causa dell’estrema densità di cristalli eterogenei, le prestazioni complessive e l’efficienza energetica della soluzione e delle interfacce saranno addirittura superiori rispetto al caso di una soluzione monolitica.

Per la prima volta, la tecnologia Co-EMIB potrebbe essere utilizzata per produrre processori ibridi Intel per il supercomputer Aurora, la cui commercializzazione è prevista per la fine del 2021 (un progetto congiunto tra Intel e Cray). Il prototipo del processore è stato mostrato al SEMICON West come una pila di 18 piccoli die su un grande die (Foveros), un paio dei quali erano collegati orizzontalmente da un'interconnessione EMIB.

La seconda delle tre nuove tecnologie di packaging spaziale dei chip di Intel si chiama Omni-Directional Interconnect (ODI). Questa tecnologia non è altro che l'utilizzo delle interfacce EMIB e Foveros per il collegamento elettrico orizzontale e verticale dei cristalli. Ciò che ha reso ODI un elemento separato è stato il fatto che l'azienda ha implementato l'alimentazione per i chiplet nello stack utilizzando connessioni TSV verticali. Questo approccio consentirà di distribuire efficacemente il cibo. Allo stesso tempo, la resistenza dei canali TSV da 70 μm per l'alimentazione è notevolmente ridotta, il che ridurrà il numero di canali necessari per fornire energia e libererà spazio sul chip per i transistor (ad esempio).

Infine, Intel ha definito l'interfaccia chip-to-chip MDIO la terza tecnologia per il packaging spaziale. Si tratta dell'Advanced Interface Bus (AIB) sotto forma di strato fisico per lo scambio di segnali tra chip. A rigor di termini, questa è la seconda generazione del bus AIB, che Intel sta sviluppando per DARPA. La prima generazione di AIB è stata introdotta nel 2017 con la possibilità di trasferire dati su ciascun contatto ad una velocità di 2 Gbit/s. Il bus MDIO garantirà lo scambio ad una velocità di 5,4 Gbit/s. Questo collegamento diventerà un concorrente del bus TSMC LIPINCON. La velocità di trasferimento LIPINCON è più alta - 8 Gbit/s, ma Intel MDIO ha una densità GB/s per millimetro più alta: 200 contro 67, quindi Intel rivendica uno sviluppo che non è peggiore di quello del suo concorrente.

Fonte: 3dnews.ru