I arkitekturen til x86-plattformer har det dukket opp to trender som utfyller hverandre. I følge en versjon må vi bevege oss mot å integrere databehandlings- og kontrollressurser i én brikke. Den andre tilnærmingen fremmer ansvarsfordeling: prosessoren er utstyrt med en høyytelsesbuss som danner et perifert skalerbart økosystem. Den danner grunnlaget for Intel C620 systemlogikktopologien for plattformer på høyt nivå.

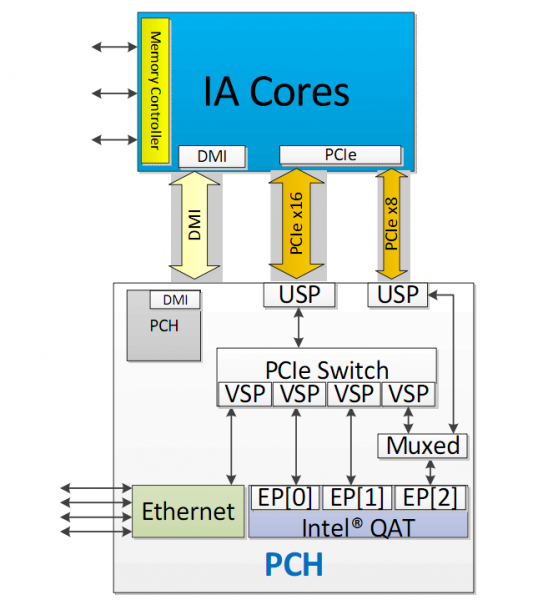

Den grunnleggende forskjellen fra det forrige Intel C610-brikkesettet er utvidelsen av kommunikasjonskanalen mellom prosessoren og periferiutstyret som er inkludert i PCH-brikken gjennom bruk av PCIe-koblinger sammen med den tradisjonelle DMI-bussen.

La oss se nærmere på innovasjonene til Intel Lewisburg sørbro: hvilke evolusjonære og revolusjonerende tilnærminger har utvidet kreftene i kommunikasjon med prosessorer?

Evolusjonære endringer i CPU-PCH-kommunikasjon

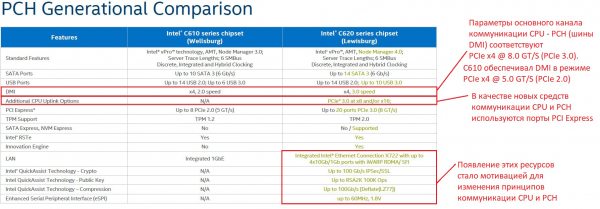

Som en del av den evolusjonære tilnærmingen fikk hovedkommunikasjonskanalen mellom CPU og sørbroen, som er DMI (Direct Media Interface)-bussen, støtte for PCIe x4 Gen3-modus med en ytelse på 8.0 GT/S. Tidligere, i Intel C610 PCH, ble kommunikasjon mellom prosessoren og systemlogikken utført i PCIe x4 Gen 2-modus med 5.0 GT/S båndbredde.

Sammenligning av systemlogikkfunksjonaliteten til Intel C610 og C620

Merk at dette undersystemet er mye mer konservativt enn de innebygde PCIe-portene til prosessoren, vanligvis brukt til å koble til GPUer og NVMe-stasjoner, hvor PCIe 3.0 har vært brukt i lang tid og overgangen til PCI Express Gen4 er planlagt.

Revolusjonerende endringer i CPU-PCH kommunikasjon

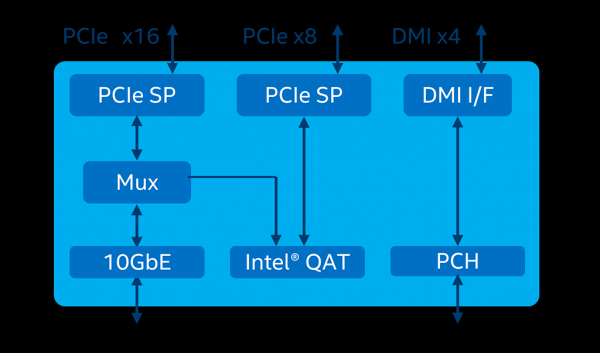

Revolusjonerende endringer inkluderer tillegg av nye PCIe CPU-PCH kommunikasjonskanaler, kalt Ekstra oppkoblinger. Fysisk er dette to PCI Express-porter som opererer i PCIe x8 Gen3- og PCIe x16 Gen3-modus, begge 8.0 GT/S.

For interaksjon mellom CPU og Intel C620 PCH brukes 3 busser: DMI og to PCI Express-porter

Hvorfor var det nødvendig å revidere den eksisterende kommunikasjonstopologien med Intel C620? For det første kan opptil 4x 10GbE nettverkskontrollere med RDMA-funksjonalitet integreres i PCH. For det andre er den nye og raskere generasjonen av Intel QuickAssist Technology (QAT)-koprosessorer, som gir maskinvarestøtte for komprimering og kryptering, ansvarlig for kryptering av nettverkstrafikk og utveksling med lagringsundersystemet. Og til slutt, "innovasjonsmotoren" - , som bare vil være tilgjengelig for OEM-er.

Skalerbarhet og fleksibilitet

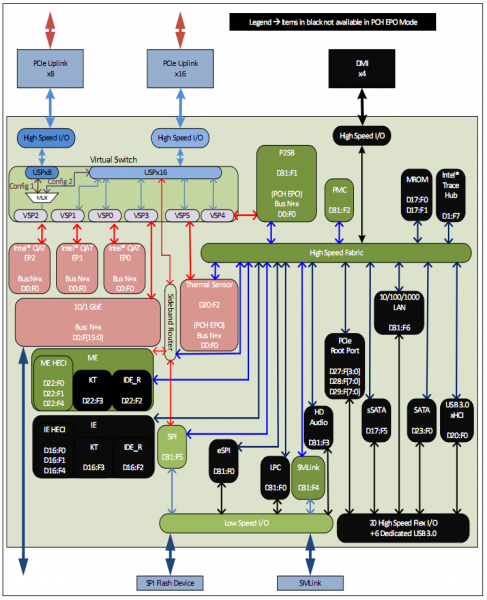

En viktig egenskap er muligheten til valgfritt å velge ikke bare PCH-forbindelsestopologien, men også prioriteringene til de interne ressursene til brikken i tilgang til høyhastighetskommunikasjonskanaler med sentralprosessoren (prosessorer). I tillegg, i den spesielle EPO (EndPoint Only Mode), utføres PCH-tilkoblingen i statusen til en vanlig PCI Express-enhet som inneholder 10 GbE-ressurser og Intel QAT. Samtidig er det klassiske DMI-grensesnittet, samt en rekke Legacy-delsystemer, vist i svart i diagrammet, deaktivert.

Intern arkitektur for Intel C620 PCH-brikken

I teorien gjør dette det mulig å bruke mer enn én Intel C620 PCH-brikke i et system, og skalere 10 GbE og Intel QAT-funksjonalitet for å møte ytelseskravene. Samtidig kan Legacy-funksjoner som bare trengs i en enkelt kopi aktiveres kun på en av de installerte PCH-brikkene.

Så det siste ordet i design vil tilhøre plattformutvikleren, som handler på grunnlag av både teknologiske og markedsføringsfaktorer i samsvar med plasseringen av hvert spesifikt produkt.

Kilde: www.habr.com