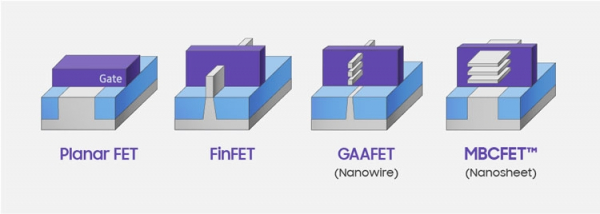

Hoje Samsung Eletrônica sobre planos de desenvolvimento de processos técnicos para produção de semicondutores. A empresa considera a criação de projetos digitais de chips experimentais de 3 nm baseados em transistores MBCFET patenteados a principal conquista atual. Estes são transistores com múltiplos canais nanopage horizontais em portas FET verticais (Multi-Bridge-Channel FET).

Como parte de uma aliança com a IBM, a Samsung desenvolveu uma tecnologia ligeiramente diferente para a produção de transistores com canais totalmente cercados por portas (GAA ou Gate-All-Around). Os canais deveriam ser finos na forma de nanofios. Posteriormente, a Samsung se afastou desse esquema e patenteou uma estrutura de transistor com canais em forma de nanopáginas. Esta estrutura permite controlar as características dos transistores manipulando tanto o número de páginas (canais) quanto ajustando a largura das páginas. Para a tecnologia FET clássica, tal manobra é impossível. Para aumentar a potência de um transistor FinFET, é necessário multiplicar o número de aletas FET no substrato, e isso requer área. As características do transistor MBCFET podem ser alteradas dentro de uma porta física, para a qual é necessário definir a largura dos canais e seu número.

A disponibilidade de um design digital (gravado) de um protótipo de chip para produção usando o processo GAA permitiu à Samsung determinar os limites das capacidades dos transistores MBCFET. Deve-se ter em mente que estes ainda são dados de modelagem computacional e o novo processo técnico só pode ser julgado finalmente após ter sido lançado na produção em massa. No entanto, existe um ponto de partida. A empresa afirmou que a transição do processo de 7 nm (obviamente a primeira geração) para o processo GAA proporcionará uma redução de 45% na área da matriz e uma redução de 50% no consumo. Se você não economizar no consumo, a produtividade pode aumentar em 35%. Anteriormente, a Samsung via economias e ganhos de produtividade ao migrar para o processo de 3nm separados por vírgulas. Acontece que era um ou outro.

A empresa considera a preparação de uma plataforma de nuvem pública para desenvolvedores independentes de chips e empresas sem fábrica um ponto importante na popularização da tecnologia de processo de 3 nm. A Samsung não escondeu o ambiente de desenvolvimento, verificação de projetos e bibliotecas em servidores de produção. A plataforma SAFE (Samsung Advanced Foundry Ecosystem Cloud) estará disponível para designers de todo o mundo. A plataforma de nuvem SAFE foi criada com a participação dos principais serviços de nuvem pública, como Amazon Web Services (AWS) e Microsoft Azure. Os desenvolvedores de sistemas de design da Cadence e Synopsys forneceram suas ferramentas de design no SAFE. Isso promete tornar mais fácil e barato a criação de novas soluções para os processos da Samsung.

Voltando à tecnologia de processo de 3nm da Samsung, acrescentamos que a empresa apresentou a primeira versão de seu pacote de desenvolvimento de chips - 3nm GAE PDK Versão 0.1. Com sua ajuda, você pode começar a projetar soluções de 3 nm hoje, ou pelo menos se preparar para atender a esse processo da Samsung quando ele se tornar generalizado.

A Samsung anuncia seus planos futuros da seguinte forma. No segundo semestre deste ano, será lançada a produção em massa de chips utilizando o processo de 6nm. Ao mesmo tempo, o desenvolvimento da tecnologia de processo de 4 nm será concluído. O desenvolvimento dos primeiros produtos Samsung utilizando o processo de 5 nm será concluído neste outono, com o lançamento da produção no primeiro semestre do próximo ano. Além disso, até o final deste ano, a Samsung concluirá o desenvolvimento da tecnologia de processo 18FDS (18 nm em wafers FD-SOI) e chips eMRAM de 1 Gbit. As tecnologias de processo de 7 nm a 3 nm usarão scanners EUV com intensidade crescente, fazendo com que cada nanômetro conte. Mais adiante, cada passo será dado com luta.

Fonte: 3dnews.ru