В архітектурі x86-платформ виникли дві течії, що взаємно доповнюють одна одну. За однією версією, необхідно рухатися у бік інтеграції щодо одного кристалі обчислювальних і управляючих ресурсів. Другий підхід сповідує розподіл обов'язків: процесор оснащується продуктивною шиною, що формує периферійну екосистему, що масштабується. Він покладено основою топології системної логіки Intel C620 для високорівневих платформ.

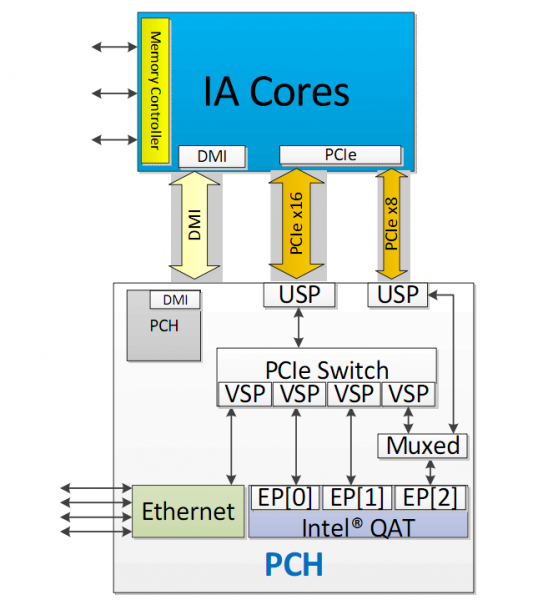

Принципова відмінність від попереднього чіпсету Intel C610 полягає у розширенні каналу комунікації процесора з периферією, що входить до складу мікросхеми PCH, за рахунок використання PCIe-лінків поряд із традиційною DMI-шиною.

Розглянемо докладніше нововведення південного мосту Intel Lewisburg: якими еволюційними та революційними підходами розширено його повноваження у комунікації з процесорами?

Еволюційні зміни у комунікації CPU-PCH

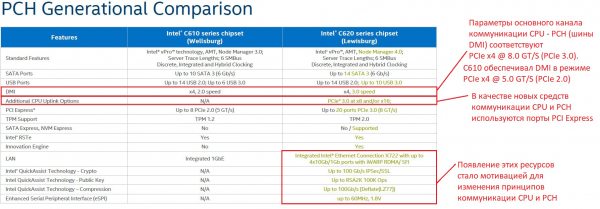

В рамках еволюційного підходу основний канал зв'язку CPU з південним мостом, яким є шина DMI (Direct Media Interface), отримав підтримку PCIe x4 Gen3 з продуктивністю 8.0 GT/S. Раніше, в Intel C610 PCH комунікація процесора та системної логіки виконувалася в режимі PCIe x4 Gen 2 у смузі пропускання 5.0 GT/S.

Порівняння функціональності системної логіки Intel C610 та C620

Зауважимо, ця підсистема значно консервативніша, ніж вбудовані PCIe-порти процесора, які зазвичай використовуються для підключення GPU і NVMe накопичувачів, де вже давно застосовується PCIe 3.0 і намічений перехід до PCI Express Gen4.

Революційні зміни у комунікації CPU-PCH

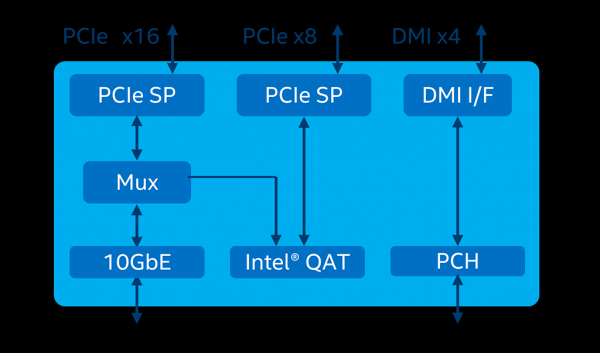

До революційних змін можна віднести додавання нових PCIe-каналів комунікації CPU-PCH, які називають Additional Uplinks. Фізично це два порти PCI Express, що працюють в режимах PCIe x8 Gen3 і PCIe x16 Gen3, обидва - 8.0 GT/S.

Для взаємодії CPU та Intel C620 PCH використовуються 3 шини: DMI та два порти PCI Express

Заради чого потрібен був перегляд існуючої топології комунікацій з Intel C620? По-перше, у складі PCH може бути інтегровано до 4x мережевих контролерів 10GbE з функціональністю RDMA. По-друге, за шифрування мережного трафіку та обміну з підсистемою зберігання відповідає нове та швидше покоління співпроцесорів Intel QuickAssist Technology (QAT), що забезпечують апаратну підтримку компресії та криптування. І, нарешті, «двигун інновацій» , який буде доступний тільки для виробників OEM.

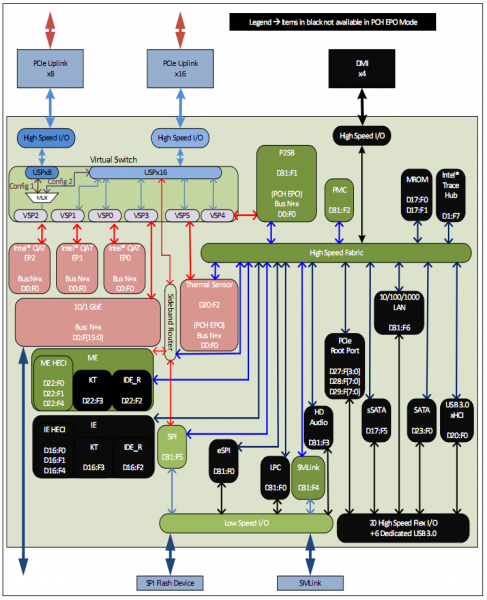

Масштабируемость і гибкость

Важливою властивістю є можливість опціонального вибору як топології підключення PCH, а й пріоритетів внутрішніх ресурсів мікросхеми у доступі до швидкісних каналів зв'язку з центральним процесором (процесорами). Крім того, у спеціальному режимі EPO (EndPoint Only Mode), підключення PCH здійснюється у статусі звичайного PCI Express пристрою, що містить ресурси 10 GbE та Intel QAT. При цьому класичний інтерфейс DMI, а також ряд Legacy-підсистем, що показані на діаграмі чорним кольором, відключені.

Внутрішня архітектура мікросхеми Intel C620 PCH

Теоретично, це дає можливість використовувати в системі більше однієї мікросхеми Intel C620 PCH, масштабуючи функціональність 10 GbE та Intel QAT відповідно до вимог продуктивності. У цьому Legacy функції, необхідні лише у єдиному екземплярі, може бути включені лише в одній із встановлених мікросхем PCH.

Отже, фінальне слово в дизайні належатиме розробнику платформи, що діє на основі як технологічних, так і маркетингових факторів відповідно до позиціонування кожного конкретного продукту.

Джерело: habr.com