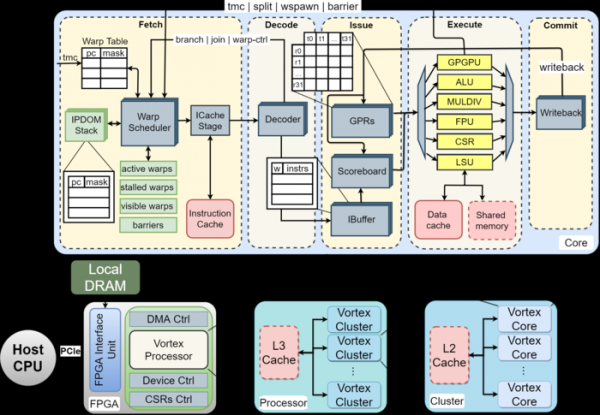

ສະບັບທີສອງຂອງໂຄງການ Vortex ໄດ້ຖືກຈັດພີມມາ, ການພັດທະນາ GPGPU ເປີດໂດຍອີງໃສ່ສະຖາປັດຕະຍະກໍາຊຸດຄໍາແນະນໍາ RISC-V, ອອກແບບເພື່ອປະຕິບັດຄອມພິວເຕີ້ຂະຫນານໂດຍໃຊ້ OpenCL API ແລະຮູບແບບການປະຕິບັດ SIMT (ຄໍາແນະນໍາດຽວ, ຫຼາຍກະທູ້). ໂຄງການດັ່ງກ່າວຍັງສາມາດຖືກນໍາໃຊ້ເພື່ອດໍາເນີນການຄົ້ນຄ້ວາໃນຂົງເຂດຂອງກາຟິກ 3D ແລະພັດທະນາສະຖາປັດຕະຍະກໍາ GPU ໃຫມ່. ຮູບແບບ, ລາຍລະອຽດຂອງຕັນຮາດແວໃນພາສາ Verilog, simulator, ໄດເວີ ແລະເອກະສານການອອກແບບທີ່ມາພ້ອມກັບແມ່ນແຈກຢາຍພາຍໃຕ້ໃບອະນຸຍາດ Apache 2.0.

ຫຼັກຂອງ GPGPU ແມ່ນ RISC-V ISA ທົ່ວໄປ, ຂະຫຍາຍດ້ວຍຄໍາແນະນໍາເພີ່ມເຕີມບາງຢ່າງທີ່ຈໍາເປັນເພື່ອສະຫນັບສະຫນູນການເຮັດວຽກ GPU ແລະການຄວບຄຸມ thread. ໃນຂະນະດຽວກັນ, ການປ່ຽນແປງໃນສະຖາປັດຕະຍະກໍາຊຸດຄໍາແນະນໍາ RISC-V ໄດ້ຖືກເກັບຮັກສາໄວ້ເປັນຕໍາ່ສຸດທີ່ແລະ, ເມື່ອໃດກໍ່ຕາມທີ່ເປັນໄປໄດ້, ຄໍາແນະນໍາ vector ທີ່ມີຢູ່ແລ້ວແມ່ນຖືກນໍາໃຊ້. ວິທີການທີ່ຄ້າຍຄືກັນແມ່ນໃຊ້ໃນໂຄງການ RV64X, ເຊິ່ງຍັງພັດທະນາ GPU ເປີດໂດຍອີງໃສ່ເຕັກໂນໂລຢີ RISC-V.

ສໍາລັບກາຟິກທີ່ອີງໃສ່ເທກໂນໂລຍີ Vortex, GPU Skybox ເປີດກໍາລັງຖືກພັດທະນາ, ສະຫນັບສະຫນູນ Vulkan graphics API. ຕົ້ນແບບ Skybox, ສ້າງຂຶ້ນບົນພື້ນຖານຂອງ Altera Stratix 10 FPGA ແລະລວມທັງ 32 cores (512 threads), ເຮັດໃຫ້ມັນເປັນໄປໄດ້ທີ່ຈະບັນລຸການປະຕິບັດການຕື່ມຂໍ້ມູນຂອງ 230 gigapixels ຕໍ່ວິນາທີ (3.7 gigatransactions ຕໍ່ວິນາທີ) ທີ່ຄວາມຖີ່ຂອງ 29.4 MHz. ມັນໄດ້ຖືກສັງເກດເຫັນວ່ານີ້ແມ່ນ GPU ເປີດທໍາອິດທີ່ມີຊອບແວແລະການປະຕິບັດຮາດແວທີ່ສະຫນັບສະຫນູນ Vulkan.

ຄຸນນະສົມບັດຕົ້ນຕໍຂອງ Vortex:

- ຮອງຮັບ 32- ແລະ 64-bit RISC-V instruction set architectures RV32IMF ແລະ RV64IMAFD.

- ຈໍານວນຂອງຫຼັກການກໍານົດໄດ້, ຕັນວຽກງານ (warps) ແລະກະທູ້.

- ຈໍານວນທີ່ສາມາດກໍານົດໄດ້ຂອງ ALUs, FPUs, LSUs ແລະ SFUs ຕໍ່ຫຼັກ.

- ຄວາມກວ້າງຂອງບັນຫາທໍ່ສາມາດປັບໄດ້.

- ຫນ່ວຍຄວາມຈໍາທີ່ໃຊ້ຮ່ວມກັນທາງເລືອກແລະ L1, L2 ແລະ L3 cache.

- ຮອງຮັບສະເພາະ OpenCL 1.2.

- ຄວາມເປັນໄປໄດ້ຂອງການປະຕິບັດໂດຍອີງໃສ່ FPGA Altera Arria 10, Altera Stratix 10, Xilinx Alveo U50, U250, U280 ແລະ Xilinx Versal VCK5000.

- ຄໍາແນະນໍາຂັ້ນສູງ: "tex" ເພື່ອເລັ່ງການປຸງແຕ່ງໂຄງສ້າງ, vx_rast ເພື່ອຄວບຄຸມ rasterization, vx_rop ເພື່ອຈັດການຊິ້ນສ່ວນ, ຄວາມເລິກແລະຄວາມໂປ່ງໃສ, vx_imadd ເພື່ອປະຕິບັດການຄູນແລະເພີ່ມການດໍາເນີນງານ, vx_wspawn, vx_tmc ແລະ vx_bar ເພື່ອເປີດໃຊ້ຂອບຄໍາແນະນໍາແລະ wavefronts, ຊຸດຂອງກະທູ້ ປະຕິບັດໃນຂະຫນານໂດຍ SIMD Engine), vx_split ແລະ vx_join.

- ການສະຫນັບສະຫນູນການເປັນຕົວແທນລະດັບປານກາງຂອງ SPIR-V shaders ແມ່ນປະຕິບັດຜ່ານການແປເປັນ OpenCL.

- ສໍາລັບການພັດທະນາແອັບພລິເຄຊັນ, ຊຸດເຄື່ອງມືໄດ້ຖືກສະເຫນີ, ລວມທັງຕົວແປຂອງ PoCL (compiler ແລະ runtime OpenCL), LLVM/Clang, GCC ແລະ Binutils ດັດແປງສໍາລັບການເຮັດວຽກກັບ Vortex.

- ການຈຳລອງຊິບແມ່ນຮອງຮັບໂດຍໃຊ້ Verilator (Verilog simulator), RTLSIM (ການຈຳລອງ RTL) ແລະ SimX (ການຈຳລອງຊອບແວ).

ໃນບັນດາການປ່ຽນແປງໃນ Vortex 2.0:

- ສະຖາປັດຕະຍະກຳຈຸລະພາກໄດ້ຮັບການປັບປຸງໃຫ້ເໝາະສົມ.

- ເພີ່ມການສະຫນັບສະຫນູນສໍາລັບສະຖາປັດຕະຍະກໍາຊຸດຄໍາແນະນໍາ RISC-V RV64IMAFD 64-bit.

- ເພີ່ມຄວາມເປັນໄປໄດ້ຂອງການປະຕິບັດໂດຍອີງໃສ່ Xilinx FPGA.

- ເພີ່ມການສະຫນັບສະຫນູນສໍາລັບ LLVM 16 ແລະ Ubuntu 20.04.

- ການສະທ້ອນຄືນໄດ້ຖືກປະຕິບັດແລະຂໍ້ບົກພ່ອງທີ່ຖືກກໍານົດໃນລະຫວ່າງການປະເມີນຄຸນນະພາບໄດ້ຖືກແກ້ໄຂ.

ແຫຼ່ງຂໍ້ມູນ: opennet.ru