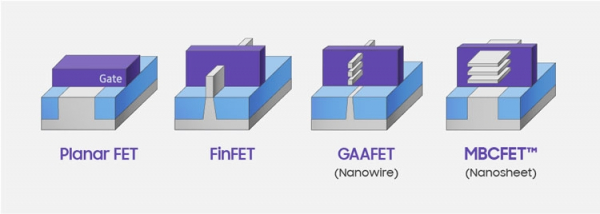

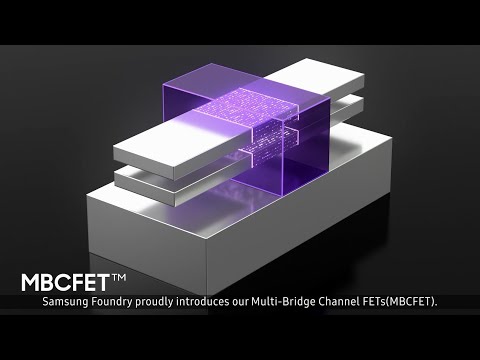

Danes Samsung Electronics o načrtih za razvoj tehničnih procesov za proizvodnjo polprevodnikov. Podjetje meni, da je glavni trenutni dosežek ustvarjanje digitalnih projektov eksperimentalnih 3-nm čipov, ki temeljijo na patentiranih tranzistorjih MBCFET. To so tranzistorji z več vodoravnimi nanostraničnimi kanali v navpičnih FET vratih (Multi-Bridge-Channel FET).

Samsung je v okviru zavezništva z IBM razvil nekoliko drugačno tehnologijo za proizvodnjo tranzistorjev s kanali, popolnoma obdanimi z vrati (GAA ali Gate-All-Around). Kanale naj bi naredili tanke v obliki nanožic. Kasneje se je Samsung odmaknil od te sheme in patentiral strukturo tranzistorja s kanali v obliki nanostrani. Ta struktura vam omogoča nadzor nad značilnostmi tranzistorjev z manipulacijo števila strani (kanalov) in prilagajanjem širine strani. Za klasično FET tehnologijo je takšen manever nemogoč. Za povečanje moči tranzistorja FinFET je treba pomnožiti število reber FET na substratu, kar zahteva površino. Karakteristike tranzistorja MBCFET je mogoče spreminjati znotraj enih fizičnih vrat, za kar je treba nastaviti širino kanalov in njihovo število.

Razpoložljivost digitalnega dizajna (posnetega) prototipa čipa za proizvodnjo z uporabo postopka GAA je Samsungu omogočila določitev meja zmogljivosti tranzistorjev MBCFET. Zavedati se je treba, da gre še vedno za podatke računalniškega modeliranja in da lahko nov tehnični postopek dokončno presojamo šele, ko ga uvedemo v množično proizvodnjo. Vendar pa obstaja izhodišče. Podjetje je dejalo, da bo prehod s 7nm procesa (očitno prve generacije) na proces GAA zagotovil 45-odstotno zmanjšanje površine matrice in 50-odstotno zmanjšanje porabe. Če ne varčujete pri porabi, lahko produktivnost povečate za 35 %. Prej je Samsung pri prehodu na 3n proces dosegel prihranke in povečanje produktivnosti ločeni z vejicami. Izkazalo se je bodisi eno ali drugo.

Podjetje meni, da je priprava javne platforme v oblaku za neodvisne razvijalce čipov in podjetja, ki ne uporabljajo fabless, pomembna točka pri popularizaciji 3nm procesne tehnologije. Samsung ni skrival razvojnega okolja, preverjanja projektov in knjižnic na produkcijskih strežnikih. Platforma SAFE (Samsung Advanced Foundry Ecosystem Cloud) bo na voljo oblikovalcem po vsem svetu. Oblačna platforma SAFE je bila ustvarjena s sodelovanjem večjih javnih storitev v oblaku, kot sta Amazon Web Services (AWS) in Microsoft Azure. Razvijalci oblikovalskih sistemov Cadence in Synopsys so svoja orodja za načrtovanje zagotovili znotraj SAFE. To obljublja, da bo lažje in cenejše ustvarjanje novih rešitev za procese Samsung.

Če se vrnemo k Samsungovi 3nm procesni tehnologiji, dodajmo, da je podjetje predstavilo prvo različico svojega razvojnega paketa čipov – 3nm GAE PDK Version 0.1. Z njegovo pomočjo lahko že danes začnete oblikovati 3nm rešitve ali pa se vsaj pripravite na srečanje s tem Samsungovim procesom, ko bo postal razširjen.

Samsung napoveduje svoje načrte za prihodnost, kot sledi. V drugi polovici letošnjega leta bo stekla množična proizvodnja čipov po 6nm procesu. Hkrati bo zaključen razvoj 4nm procesne tehnologije. Razvoj prvih Samsungovih izdelkov po 5nm postopku bo zaključen to jesen, proizvodnja pa bo stekla v prvi polovici prihodnjega leta. Poleg tega bo Samsung do konca tega leta dokončal razvoj procesne tehnologije 18FDS (18 nm na rezinah FD-SOI) in 1-Gbit eMRAM čipov. Procesne tehnologije od 7 nm do 3 nm bodo uporabljale EUV skenerje z naraščajočo intenzivnostjo, pri čemer bo vsak nanometer štel. Nadalje na poti navzdol bo vsak korak narejen z bojem.

Vir: 3dnews.ru