Ua paʻi ʻia ka paʻi ʻelua o ka papahana Vortex, e hoʻomohala ana i kahi GPGPU hāmama e pili ana i ka RISC-V instruction set architecture, i hoʻolālā ʻia e hana i ka hoʻopili like ʻana me ka OpenCL API a me ka SIMT (Single Instruction, Multiple Threads) execution model. Hiki ke hoʻohana ʻia ka papahana e hana i ka noiʻi ma ke kahua o nā kiʻi 3D a hoʻomohala i nā hale kiʻi GPU hou. Hāʻawi ʻia nā papahana, nā wehewehe ʻana o nā poloka lako ma ka ʻōlelo Verilog, simulator, nā mea hoʻokele a me nā palapala hoʻolālā e hui pū ʻia ma lalo o ka laikini Apache 2.0.

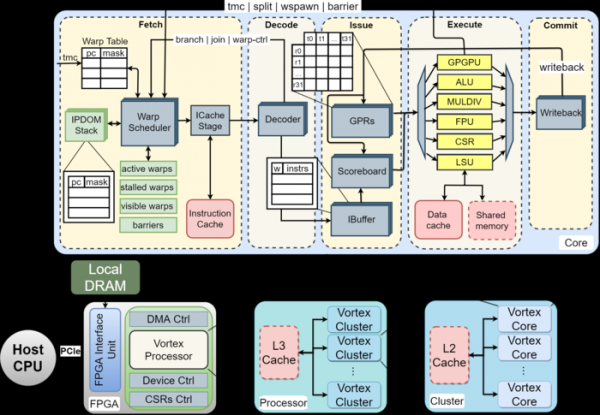

ʻO ke kumu o GPGPU he RISC-V ISA maʻamau, i hoʻonui ʻia me kekahi mau ʻōlelo aʻoaʻo e pono ai ke kākoʻo i ka hana GPU a me ka hoʻokele thread. Ma ka manawa like, mālama ʻia nā hoʻololi o ka hoʻonohonoho hoʻonohonoho hoʻonohonoho RISC-V i ka liʻiliʻi loa a, inā hiki, hoʻohana ʻia nā ʻōkuhi vector i loaʻa. Hoʻohana ʻia kahi ala like i ka papahana RV64X, kahi e hoʻomohala ai i kahi GPU hāmama e pili ana i nā ʻenehana RISC-V.

No nā kiʻi kiʻi e pili ana i nā ʻenehana Vortex, ke kūkulu ʻia nei ka Open GPU Skybox, e kākoʻo ana i ka Vulkan graphics API. ʻO ka Skybox prototype, i hana ʻia ma ke kumu o ka Altera Stratix 10 FPGA a me 32 cores (512 threads), i hiki ke hoʻokō i ka hana piha o 230 gigapixels i kekona (3.7 gigatransactions per second) ma ke alapine o 29.4 MHz. Hoʻomaopopo ʻia ʻo kēia ka GPU wehe mua me ka lako polokalamu a me nā lako lako e kākoʻo ana iā Vulkan.

ʻO nā hiʻohiʻona nui o Vortex:

- Kākoʻo ʻo 32- a me 64-bit RISC-V i ka hoʻonohonoho hoʻonohonoho hoʻonohonoho ʻana i nā hale hana RV32IMF a me RV64IMAFD.

- Ka helu o nā cores, nā poloka hana (warps) a me nā kaula.

- Helu hiki ke hoʻonohonoho ʻia o nā ALU, nā FPU, nā LSU a me nā SFU no kēlā me kēia kumu.

- ʻO ka laula hoʻopuka paipu hiki ke hoʻololi.

- Hoʻomanaʻo kaʻana like ʻole a me L1, L2 a me L3 huna.

- Kākoʻo kikoʻī OpenCL 1.2.

- Hiki ke hoʻokō ma muli o FPGA Altera Arria 10, Altera Stratix 10, Xilinx Alveo U50, U250, U280 a me Xilinx Versal VCK5000.

- Nā ʻōlelo aʻo kiʻekiʻe: "tex" e wikiwiki i ka hana ʻana, vx_rast e kāohi i ka rasterization, vx_rop e mālama i nā ʻāpana, hohonu a me ka ʻike, vx_imadd e hana multiply a hoʻohui i nā hana, vx_wspawn, vx_tmc a me vx_bar e hoʻāla i nā ʻaoʻao aʻo a me nā alo nalu , kahi o nā kaula. hana like ʻia e ka SIMD Engine), vx_split a me vx_join.

- Hoʻokō ʻia ke kākoʻo no ka hōʻike ʻana i waena o nā shaders SPIR-V ma o ka unuhi ʻana iā OpenCL.

- No ka hoʻomohala noiʻi, hāʻawi ʻia kahi hāmeʻa, me nā ʻano like ʻole o PoCL (compiler and runtime OpenCL), LLVM/Clang, GCC a me Binutils i hoʻololi ʻia no ka hana ʻana me Vortex.

- Kākoʻo ʻia ka simulation chip me ka hoʻohana ʻana i ka Verilator (Verilog simulator), RTLSIM (RTL simulation) a me SimX (software simulation).

Ma waena o nā loli ma Vortex 2.0:

- Ua hoʻonui ʻia ka microarchitecture.

- Hoʻohui ʻia ke kākoʻo no 64-bit RISC-V RV64IMAFD hoʻonohonoho hoʻonohonoho hoʻonohonoho.

- Hoʻohui i ka hiki ke hoʻokō ma muli o Xilinx FPGA.

- Hoʻohui i ke kākoʻo no LLVM 16 a me Ubuntu 20.04.

- Ua hoʻokō ʻia ka refactoring a ua hoʻoponopono ʻia nā hemahema i ʻike ʻia i ka wā o ka loiloi maikaʻi.

Source: opennet.ru