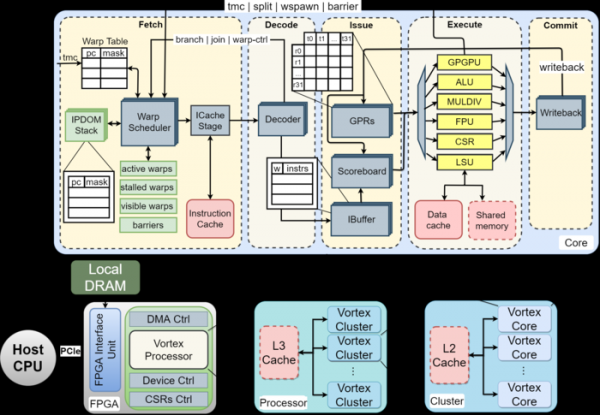

新版本的Vortex專案已經發布,開發基於RISC-V指令集架構的開放式GPGPU,旨在使用OpenCL API和SIMT(單指令、多執行緒)執行模型進行平行運算。該專案還可用於 3D 圖形領域的研究和新 GPU 架構的開發。方案、Verilog 語言硬體區塊描述、模擬器、驅動程式以及隨附的設計文件均在 Apache 2.0 授權下分發。

GPGPU 的核心是通用 RISC-V ISA,並擴展了一些支援 GPU 功能和執行緒控制所需的附加指令。 同時,RISC-V 指令集架構的變化保持在最低限度,並且盡可能使用現有的向量指令。 RV64X專案也採用了類似的方法,該專案也開發了基於RISC-V技術的開放GPU。

渦流的主要特徵:

- 支援32位元和64位元RISC-V指令集架構RV32IMF和RV64IMAFD。

- 可配置的核心數量、任務區塊(warp)和執行緒數量。

- 每個核心的 ALU、FPU、LSU 和 SFU 數量可配置。

- 可調式管道發出寬度。

- 可選共享記憶體和 L1、L2 和 L3 快取。

- OpenCL 1.2 規格支援。

- 可基於 FPGA Altera Arria 10、Altera Stratix 10、Xilinx Alveo U50、U250、U280 和 Xilinx Versal VCK5000 實作。

- 進階指令:「tex」加速紋理處理,vx_rast控制光柵化,vx_rop處理片段、深度和透明度,vx_imadd執行乘法和加法操作,vx_wspawn、vx_tmc和vx_bar激活指令邊緣和波前,一組線程由SIMD 引擎並行執行)、vx_split 和vx_join。

- 對 SPIR-V 著色器的中間表示的支援是透過轉換為 OpenCL 來實現的。

- 對於應用程式開發,提供了一個工具包,包括 PoCL(編譯器和執行時間 OpenCL)、LLVM/Clang、GCC 和適用於 Vortex 的 Binutils 的變體。

- 支援使用 Verilator(Verilog 模擬器)、RTLSIM(RTL 模擬)和 SimX(軟體模擬)進行晶片模擬。

對於基於 Vortex 技術的圖形,正在開發開放式 GPU Skybox,支援 Vulkan 圖形 API。 Skybox 原型基於 Altera Stratix 10 FPGA 創建,包含 32 個核心(512 個執行緒),能夠在 230 MHz 頻率下實現每秒 3.7 吉像素(每秒 29.4 吉比特事務)的填充效能。 值得注意的是,這是第一個支援Vulkan的軟體和硬體實現的開放GPU。

Vortex 2.1 的變化包括:

- 新增了spawn_taskgroups API,用於啟動使用本地記憶體並支援設定記憶體屏障的核心。

- 已經提出了一個新的擴充來創建可重定位的二進位核心。

- 新增了對記憶體管理 API 的 vx_mem_reserve、vx_mem_access 和 vx_mem_address 呼叫。

- 新增了新的運行時 API vx_check_ocupancy。

- GPU 驅動程式中新增了一個選項,用於在本機 GPU 上執行 OpenCL 測試。

- 新增了使用本地記憶體(psum、sgemm2、sgemm3)的 OpenCL 測試。

- 新增了專門適用於 Vortex 的 libc 和 librt 庫版本。

- 新增了對合併相鄰空閒記憶體區塊(記憶體合併)的支援。

- 微架構得到了最佳化。

- 新增了一個新的建置腳本,將來源檔案與建置目錄分開。

來源: opennet.ru