વોર્ટેક્સ પ્રોજેક્ટની બીજી આવૃત્તિ પ્રકાશિત કરવામાં આવી છે, જેમાં RISC-V સૂચના સેટ આર્કિટેક્ચર પર આધારિત ઓપન GPGPU વિકસાવવામાં આવી છે, જે OpenCL API અને SIMT (સિંગલ ઇન્સ્ટ્રક્શન, મલ્ટીપલ થ્રેડ્સ) એક્ઝેક્યુશન મોડલનો ઉપયોગ કરીને સમાંતર કમ્પ્યુટિંગ કરવા માટે રચાયેલ છે. પ્રોજેક્ટનો ઉપયોગ 3D ગ્રાફિક્સના ક્ષેત્રમાં સંશોધન કરવા અને નવા GPU આર્કિટેક્ચર્સ વિકસાવવા માટે પણ થઈ શકે છે. સ્કીમ્સ, વેરિલોગ ભાષામાં હાર્ડવેર બ્લોક્સનું વર્ણન, સિમ્યુલેટર, ડ્રાઇવરો અને તેની સાથેના ડિઝાઇન દસ્તાવેજીકરણ અપાચે 2.0 લાયસન્સ હેઠળ વિતરિત કરવામાં આવે છે.

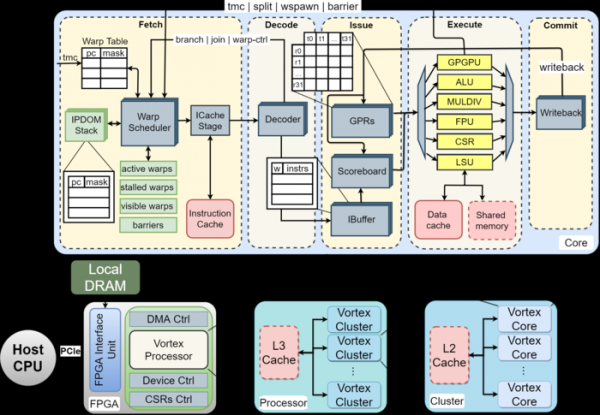

GPGPU નો મુખ્ય ભાગ એક સામાન્ય RISC-V ISA છે, જે GPU કાર્યક્ષમતા અને થ્રેડ નિયંત્રણને સમર્થન આપવા માટે જરૂરી કેટલીક વધારાની સૂચનાઓ સાથે વિસ્તૃત છે. તે જ સમયે, RISC-V સૂચના સેટ આર્કિટેક્ચરમાં ફેરફારોને ન્યૂનતમ રાખવામાં આવે છે અને જ્યારે પણ શક્ય હોય ત્યારે, હાલની વેક્ટર સૂચનાઓનો ઉપયોગ કરવામાં આવે છે. RV64X પ્રોજેક્ટમાં સમાન અભિગમનો ઉપયોગ કરવામાં આવે છે, જે RISC-V તકનીકો પર આધારિત ઓપન GPU પણ વિકસાવે છે.

વોર્ટેક્સ ટેક્નોલોજી પર આધારિત ગ્રાફિક્સ માટે, ઓપન GPU સ્કાયબોક્સ વિકસાવવામાં આવી રહ્યું છે, જે વલ્કન ગ્રાફિક્સ API ને સપોર્ટ કરે છે. અલ્ટેરા સ્ટ્રેટિક્સ 10 એફપીજીએના આધારે બનાવવામાં આવેલ અને 32 કોરો (512 થ્રેડો) સહિત, સ્કાયબોક્સ પ્રોટોટાઇપ 230 મેગાહર્ટઝની આવર્તન પર 3.7 ગીગાપિક્સેલ પ્રતિ સેકન્ડ (29.4 ગીગાટ્રાન્ઝેક્શન્સ પ્રતિ સેકન્ડ) નું ફિલ પર્ફોર્મન્સ હાંસલ કરવાનું શક્ય બનાવ્યું. તે નોંધ્યું છે કે આ સોફ્ટવેર અને હાર્ડવેર અમલીકરણ સાથેનું પ્રથમ ખુલ્લું GPU છે જે વલ્કનને સપોર્ટ કરે છે.

વોર્ટેક્સની મુખ્ય લાક્ષણિકતાઓ:

- 32- અને 64-બીટ RISC-V સૂચના સેટ આર્કિટેક્ચર્સ RV32IMF અને RV64IMAFD ને સપોર્ટ કરે છે.

- કોરો, ટાસ્ક બ્લોક્સ (વાર્પ્સ) અને થ્રેડોની રૂપરેખાંકિત સંખ્યા.

- ALUs, FPUs, LSUs અને SFU ની કોર દીઠ રૂપરેખાંકિત સંખ્યા.

- એડજસ્ટેબલ પાઇપલાઇન સમસ્યા પહોળાઈ.

- વૈકલ્પિક શેર કરેલ મેમરી અને L1, L2 અને L3 કેશ.

- OpenCL 1.2 સ્પષ્ટીકરણ સપોર્ટ.

- FPGA Altera Arria 10, Altera Stratix 10, Xilinx Alveo U50, U250, U280 અને Xilinx Versal VCK5000 પર આધારિત અમલીકરણની શક્યતા.

- અદ્યતન સૂચનાઓ: ટેક્સચર પ્રોસેસિંગને ઝડપી બનાવવા માટે "tex", રાસ્ટરાઇઝેશનને નિયંત્રિત કરવા માટે vx_rast, ટુકડાઓ, ઊંડાઈ અને પારદર્શિતાને હેન્ડલ કરવા માટે vx_rop, ગુણાકાર કરવા અને ઑપરેશન ઉમેરવા માટે vx_imadd, સૂચનાની ધારને સક્રિય કરવા માટે vx_wspawn, vx_tmc અને vx_bar, તરંગો વાંચવા માટેનો સેટ SIMD એન્જિન દ્વારા સમાંતર રીતે ચલાવવામાં આવે છે), vx_split અને vx_join.

- SPIR-V શેડરની મધ્યવર્તી રજૂઆત માટે સપોર્ટ OpenCL માં અનુવાદ દ્વારા લાગુ કરવામાં આવે છે.

- એપ્લિકેશન ડેવલપમેન્ટ માટે, એક ટૂલકિટ ઓફર કરવામાં આવે છે, જેમાં PoCL (કમ્પાઇલર અને રનટાઇમ OpenCL), LLVM/Clang, GCC અને બિનુટિલ્સનો સમાવેશ થાય છે જે વોર્ટેક્સ સાથે કામ કરવા માટે અનુકૂળ છે.

- ચિપ સિમ્યુલેશન વેરિલેટર (વેરિલોગ સિમ્યુલેટર), RTLSIM (RTL સિમ્યુલેશન) અને SimX (સોફ્ટવેર સિમ્યુલેશન) નો ઉપયોગ કરીને સપોર્ટેડ છે.

વોર્ટેક્સ 2.0 માં ફેરફારો પૈકી:

- માઇક્રોઆર્કિટેક્ચર ઑપ્ટિમાઇઝ કરવામાં આવ્યું છે.

- 64-બીટ RISC-V RV64IMAFD સૂચના સેટ આર્કિટેક્ચર માટે ઉમેરાયેલ સપોર્ટ.

- Xilinx FPGA પર આધારિત અમલીકરણની શક્યતા ઉમેરી.

- LLVM 16 અને Ubuntu 20.04 માટે સપોર્ટ ઉમેરાયો.

- રિફેક્ટરિંગ હાથ ધરવામાં આવ્યું છે અને ગુણવત્તા મૂલ્યાંકન દરમિયાન ઓળખવામાં આવેલી ખામીઓ સુધારવામાં આવી છે.

સોર્સ: opennet.ru