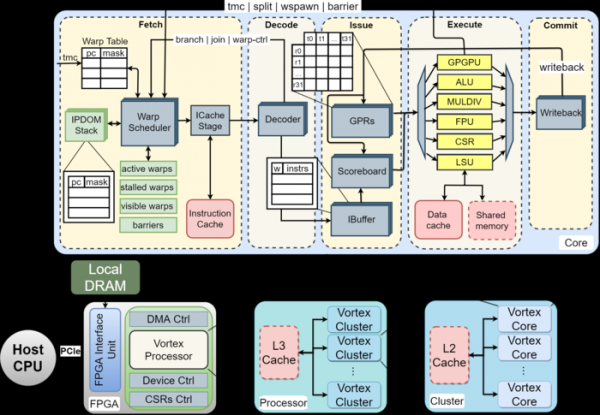

Ang ikalawang edisyon ng Vortex project ay nai-publish, na bumubuo ng isang bukas na GPGPU batay sa RISC-V instruction set architecture, na idinisenyo upang magsagawa ng parallel computing gamit ang OpenCL API at ang SIMT (Single Instruction, Multiple Threads) execution model. Magagamit din ang proyekto upang magsagawa ng pananaliksik sa larangan ng 3D graphics at bumuo ng mga bagong arkitektura ng GPU. Ang mga scheme, paglalarawan ng mga bloke ng hardware sa wikang Verilog, simulator, mga driver at kasamang dokumentasyon ng disenyo ay ipinamamahagi sa ilalim ng lisensya ng Apache 2.0.

Ang core ng GPGPU ay isang generic na RISC-V ISA, na pinalawig ng ilang karagdagang tagubilin na kailangan para suportahan ang GPU functionality at thread control. Kasabay nito, ang mga pagbabago sa arkitektura ng set ng pagtuturo ng RISC-V ay pinananatiling pinakamaliit at, hangga't maaari, ginagamit ang mga kasalukuyang tagubilin sa vector. Ang isang katulad na diskarte ay ginagamit sa proyekto ng RV64X, na bumubuo rin ng isang bukas na GPU batay sa mga teknolohiya ng RISC-V.

Para sa mga graphics batay sa mga teknolohiya ng Vortex, ang bukas na GPU Skybox ay binuo, na sumusuporta sa Vulkan graphics API. Ang Skybox prototype, na nilikha batay sa Altera Stratix 10 FPGA at kasama ang 32 cores (512 threads), ay naging posible upang makamit ang isang fill performance na 230 gigapixels per second (3.7 gigatransactions per second) sa frequency na 29.4 MHz. Ito ay nabanggit na ito ang unang bukas na GPU na may software at hardware na pagpapatupad na sumusuporta sa Vulkan.

Mga pangunahing tampok ng Vortex:

- Sinusuportahan ang 32- at 64-bit na RISC-V na mga arkitektura ng set ng pagtuturo ng RV32IMF at RV64IMAFD.

- Nako-configure ang bilang ng mga core, mga bloke ng gawain (warps) at mga thread.

- Nako-configure ang bilang ng mga ALU, FPU, LSU at SFU sa bawat core.

- Madaling iakma ang lapad ng isyu ng pipeline.

- Opsyonal na nakabahaging memorya at L1, L2 at L3 na mga cache.

- Suporta sa pagtutukoy ng OpenCL 1.2.

- Posibilidad ng pagpapatupad batay sa FPGA Altera Arria 10, Altera Stratix 10, Xilinx Alveo U50, U250, U280 at Xilinx Versal VCK5000.

- Mga advanced na tagubilin: "tex" para pabilisin ang pagpoproseso ng texture, vx_rast para makontrol ang rasterization, vx_rop para pangasiwaan ang mga fragment, depth at transparency, vx_imadd para magsagawa ng multiply at magdagdag ng mga operasyon, vx_wspawn, vx_tmc at vx_bar para i-activate ang mga gilid ng pagtuturo at wavefront , isang set ng mga thread isinagawa nang kahanay ng SIMD Engine), vx_split at vx_join.

- Ang suporta para sa intermediate na representasyon ng SPIR-V shaders ay ipinatupad sa pamamagitan ng pagsasalin sa OpenCL.

- Para sa pagbuo ng application, isang toolkit ang inaalok, kabilang ang mga variant ng PoCL (compiler at runtime OpenCL), LLVM/Clang, GCC at Binutils na inangkop para sa pakikipagtulungan sa Vortex.

- Sinusuportahan ang chip simulation gamit ang Verilator (Verilog simulator), RTLSIM (RTL simulation) at SimX (software simulation).

Kabilang sa mga pagbabago sa Vortex 2.0:

- Ang microarchitecture ay na-optimize.

- Nagdagdag ng suporta para sa 64-bit na RISC-V RV64IMAFD na arkitektura ng set ng pagtuturo.

- Idinagdag ang posibilidad ng pagpapatupad batay sa Xilinx FPGA.

- Nagdagdag ng suporta para sa LLVM 16 at Ubuntu 20.04.

- Ang refactoring ay isinagawa at ang mga depektong natukoy sa panahon ng pagtatasa ng kalidad ay naitama.

Pinagmulan: opennet.ru