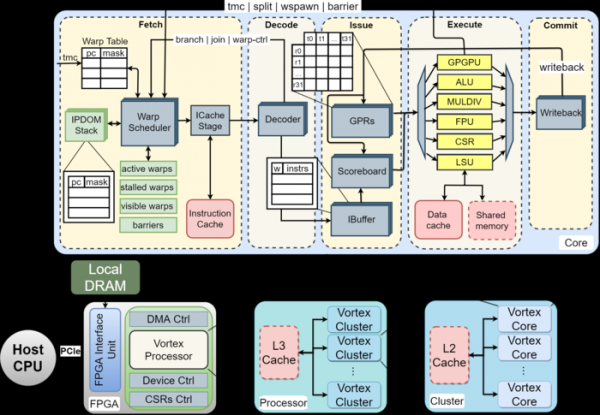

Vortex پروجیکٹ کا دوسرا ایڈیشن شائع ہو چکا ہے، جس میں RISC-V انسٹرکشن سیٹ آرکیٹیکچر پر مبنی ایک اوپن GPGPU تیار کیا گیا ہے، جسے OpenCL API اور SIMT (سنگل انسٹرکشن، ایک سے زیادہ تھریڈز) ایگزیکیوشن ماڈل کا استعمال کرتے ہوئے متوازی کمپیوٹنگ کرنے کے لیے ڈیزائن کیا گیا ہے۔ پروجیکٹ کو 3D گرافکس کے شعبے میں تحقیق کرنے اور نئے GPU فن تعمیرات کو تیار کرنے کے لیے بھی استعمال کیا جا سکتا ہے۔ اسکیمیں، ہارڈویئر بلاکس کی تفصیل ویریلوگ زبان میں، سمیلیٹر، ڈرائیورز اور اس کے ساتھ ڈیزائن کی دستاویزات اپاچی 2.0 لائسنس کے تحت تقسیم کی جاتی ہیں۔

GPGPU کا بنیادی حصہ ایک عام RISC-V ISA ہے، جس میں GPU فعالیت اور تھریڈ کنٹرول کو سپورٹ کرنے کے لیے درکار کچھ اضافی ہدایات کے ساتھ توسیع کی گئی ہے۔ ایک ہی وقت میں، RISC-V انسٹرکشن سیٹ آرکیٹیکچر میں تبدیلیوں کو کم سے کم رکھا جاتا ہے اور جب بھی ممکن ہو، موجودہ ویکٹر ہدایات استعمال کی جاتی ہیں۔ اسی طرح کا طریقہ RV64X پروجیکٹ میں استعمال کیا جاتا ہے، جو RISC-V ٹیکنالوجیز پر مبنی ایک کھلا GPU بھی تیار کرتا ہے۔

Vortex ٹیکنالوجیز پر مبنی گرافکس کے لیے، Vulkan graphics API کو سپورٹ کرتے ہوئے اوپن GPU Skybox تیار کیا جا رہا ہے۔ اسکائی باکس پروٹوٹائپ، Altera Stratix 10 FPGA کی بنیاد پر بنایا گیا اور اس میں 32 cores (512 دھاگوں) شامل ہیں، نے 230 MHz کی فریکوئنسی پر 3.7 گیگا پکسلز فی سیکنڈ (29.4 گیگا ٹرانزیکشنز فی سیکنڈ) کی فل کارکردگی حاصل کرنا ممکن بنایا۔ واضح رہے کہ یہ سافٹ ویئر اور ہارڈ ویئر کے نفاذ کے ساتھ پہلا کھلا جی پی یو ہے جو ولکن کو سپورٹ کرتا ہے۔

ورٹیکس کی اہم خصوصیات:

- 32- اور 64-bit RISC-V انسٹرکشن سیٹ آرکیٹیکچرز RV32IMF اور RV64IMAFD کو سپورٹ کرتا ہے۔

- کور، ٹاسک بلاکس (وارپس) اور تھریڈز کی قابل ترتیب تعداد۔

- ALUs، FPUs، LSUs اور SFUs کی فی کور قابل ترتیب تعداد۔

- سایڈست پائپ لائن کے مسئلے کی چوڑائی۔

- اختیاری مشترکہ میموری اور L1، L2 اور L3 کیش۔

- اوپن سی ایل 1.2 تفصیلات کی حمایت۔

- FPGA Altera Arria 10, Altera Stratix 10, Xilinx Alveo U50, U250, U280 اور Xilinx Versal VCK5000 پر مبنی نفاذ کا امکان۔

- اعلی درجے کی ہدایات: ٹیکسچر پروسیسنگ کو تیز کرنے کے لیے "tex"، راسٹرائزیشن کو کنٹرول کرنے کے لیے vx_rast، ٹکڑوں کو ہینڈل کرنے کے لیے vx_rop، گہرائی اور شفافیت، vx_imadd ضرب لگانے اور آپریشنز شامل کرنے کے لیے، vx_wspawn، vx_tmc اور vx_bar ہدایات کے کناروں کو چالو کرنے کے لیے، ویو فرون کا ایک سیٹ اور پڑھنا۔ SIMD انجن کے ذریعے متوازی طور پر عمل میں لایا گیا)، vx_split اور vx_join۔

- SPIR-V شیڈرز کی درمیانی نمائندگی کے لیے تعاون کو OpenCL میں ترجمہ کے ذریعے لاگو کیا جاتا ہے۔

- ایپلیکیشن ڈویلپمنٹ کے لیے، ایک ٹول کٹ پیش کی جاتی ہے، جس میں PoCL (مرتب کرنے والا اور رن ٹائم اوپن سی ایل)، LLVM/Clang، GCC اور Binutils کی مختلف قسمیں شامل ہیں جو Vortex کے ساتھ کام کرنے کے لیے موافق ہیں۔

- چپ سمولیشن کو Verilator (Verilog simulator)، RTLSIM (RTL simulation) اور SimX (سافٹ ویئر سمولیشن) کا استعمال کرتے ہوئے سپورٹ کیا جاتا ہے۔

ورٹیکس 2.0 میں تبدیلیوں میں سے:

- مائیکرو آرکیٹیکچر کو بہتر بنایا گیا ہے۔

- 64 بٹ RISC-V RV64IMAFD انسٹرکشن سیٹ آرکیٹیکچر کے لیے معاونت شامل کی گئی۔

- Xilinx FPGA کی بنیاد پر عمل درآمد کا امکان شامل کیا گیا۔

- LLVM 16 اور Ubuntu 20.04 کے لیے تعاون شامل کیا گیا۔

- ری فیکٹرنگ کی گئی ہے اور معیار کی تشخیص کے دوران جن نقائص کی نشاندہی کی گئی ہے ان کو درست کر دیا گیا ہے۔

ماخذ: opennet.ru