Des chercheurs de l'ETH Zurich ont développé un système de test de fuzzing appelé Cascade, visant à identifier les erreurs et les vulnérabilités des processeurs basés sur l'architecture RISC-V. Les outils ont déjà identifié 37 erreurs dans les processeurs, dont 29 ont été classées comme vulnérabilités jusqu'alors inconnues.

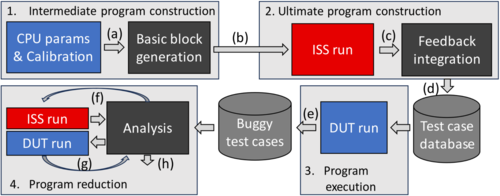

Les développeurs de Cascade ont tenté de prendre en compte les lacunes des systèmes de test de fuzzing de processeur existants, qui se limitaient à exécuter uniquement de courtes portions de code, couvrant une petite partie du jeu d'instructions et un nombre limité de combinaisons d'exécution de commandes. Cascade vise à générer des programmes volumineux et complexes qui couvrent des flux d'instructions non triviaux et entraînent des états de processeur atypiques. Dans Cascade, en utilisant le modèle de référence existant du jeu d'instructions RISC-V (RISC-V ISA), des flux d'exécution aléatoires et interconnectés (flux de contrôle) et des flux de données (flux de données) corrects sont initialement formés.

L'exécution et les flux de données dans le programme généré sont étroitement liés, donc si une erreur se produit dans le flux de données pendant l'exécution, elle se répercutera sur la progression ultérieure de l'exécution et modifiera très probablement le flux d'exécution, ce qui conduira à un achèvement incomplet. du programme. Pour identifier les instructions problématiques dans les programmes inachevés, Cascade élague automatiquement le programme en cours d'exécution au fil du temps jusqu'à ce qu'il trouve l'ensemble minimum d'instructions à l'origine de l'erreur. Cette approche est beaucoup plus facile à mettre en œuvre et plus rapide que les méthodes classiques de détection d'erreurs basées sur la réconciliation des états après chaque instruction exécutée après l'exécution réelle sur le CPU et après l'exécution à l'aide d'un modèle de référence.

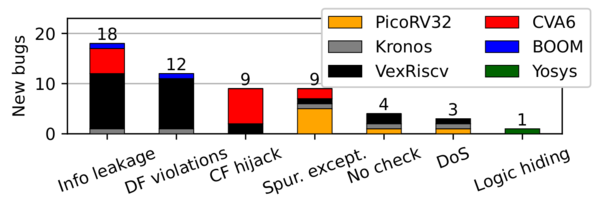

À l'aide de Cascade, cinq processeurs basés sur l'architecture RISC-V ont été testés : Kronos, PicoRV32, VexRiscv, CVA6 et BOOM, dans lesquels un total de 37 erreurs ont été identifiées. La plupart des bugs ont entraîné des problèmes de sécurité, par exemple certains problèmes ont provoqué un déni de service ou une fuite d'informations en raison de l'exécution spéculative d'instructions par un utilisateur non privilégié.

- 12 erreurs ont conduit à une violation de l'intégrité du flux de données, qui pourrait être utilisé pour modifier le résultat de certains calculs dans le code d'un autre utilisateur lorsque l'attaquant formait un certain état de structures microarchitecturales. Par exemple, un bug d'arrondi dynamique dans CPU BOOM permettait à un attaquant de forcer le processus victime à utiliser un mode d'arrondi à virgule flottante différent.

- 18 erreurs ont entraîné une fuite d'informations, qui, par exemple, ont permis à un attaquant d'accéder par canal secondaire à l'état des indicateurs et des registres FPU.

- 9 erreurs ont permis d'intercepter le flux d'exécution, ce qui a permis à un attaquant d'influencer l'exécution d'un autre programme. Par exemple, un bug dans le processeur CVA6 a conduit à la définition d'indicateurs incorrects qui ont affecté le résultat des calculs ou la détection de débordements, et un bug dans les processeurs VexRiscv dans certaines conditions a conduit à une exécution incorrecte des opérations de comparaison de registres.

- 9 erreurs étaient liées à la génération de fausses exceptions, qui pourraient être utilisées par des attaquants pour contourner les modes d'isolation utilisés dans les environnements TEE (Trusted Execution Environment). Par exemple, la lecture de certains registres CSR (Control and Status Register) a conduit à une exception, qui a permis à l'attaquant de simuler une interaction avec l'environnement.

- 4 erreurs étaient causées par un manque de contrôles appropriés et permettaient à un attaquant de contourner les contrôles liés à la sécurité (par exemple, les contrôles de l'utilisation du FPU par d'autres noyaux), de déformer les capacités disponibles du processeur ou de tromper les analyseurs.

- Trois erreurs ont provoqué le blocage du processeur lors de l'exécution de certaines manipulations à n'importe quel niveau de privilège.

- Un bug est classé comme la possibilité d'intégrer une logique cachée au stade de la conception de la puce. Le problème est présent dans le package open source Yosys, conçu pour la synthèse de niveau de transfert de registre (RTL) et utilisé dans la conception et l'émulation de processeur. L'erreur a conduit à la synthèse d'une logique incorrecte dans le FPU du processeur CVA6. Un développeur malveillant pourrait utiliser ce problème pour introduire un bug caché dans une conception qui utilise Yosys pour la synthèse logique en transmettant une description RTL (Register Transfer Layer) apparemment anodine.

- Les erreurs non liées à la sécurité incluent des problèmes avec les compteurs de performances des processeurs Kronos, VexRiscv et BOOM, qui entraînent des distorsions lors du comptage des instructions.

Source: opennet.ru